I enjoy learning and writing about new technologies closely connected to our personal and working lives (the kind you could explain to your Mom or a neighbor). So naturally I’m interested in AI, communication and security as applied to the home automation, transportation, virtual, augmented and mixed reality, industry and so… Read More

WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More

WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More

WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read More

Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read MoreeSilicon Brings a New Software Interface to its 7nm neuASIC Machine Learning Platform at Hot Chips

In early May of this year, eSilicon announced the tape-out of a test chip which included the latest additions to its neuASIC™ IP platform. At the upcoming Hot Chips Symposium to be held at Stanford on August 19 and 20, 2019, eSilicon will be demonstrating the software component of this AI-enabling IP platform. At the event, eSilicon… Read More

Accelerate Your Early Design Recon

A product launch nowadays demands shorter runway. SoC designers challenges are not so much in facing the unavailability of proven design capture methodologies or IP’s that could satisfy their product requirements, but more so in orchestrating the integration of all those components to deliver the targeted functionalities… Read More

Webinar: Designing Complex SoCs and Dealing with Multiple File Formats

In SoC design it’s all about managing complexity through modeling, and the models that make up IC designs come in a wide range of file formats like:

- Transistor-level , SPICE

- Interconnect parasitics, SPEF

- Gate and RTL, Verilog, VHDL

Even with standard file formats, designers still have to traverse the hierarchy to find out… Read More

Steve Jobs, NeXT Computer, and Apple

From time to time I give presentations to various audiences: Silicon Valley the Way I Saw It. I always enjoy doing that. One particular section always makes me stop and think. “Who was this guy? How did he do what he did? Why didn’t I do that? “What made him so special?” It’s the Steve Jobs section. I met twice with Steve Jobs when … Read More

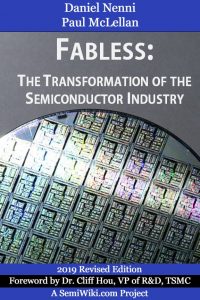

Webinar – Fabless: The Transformation of the Semiconductor Industry 2019 Update!

As more than 343 people (and counting) know, we will be releasing the 2019 updated PDF version of our first book “Fabless: The Transformation of the Semiconductor Industry” via handout at a live webinar. The response has been overwhelming and I want to personally thank you. The webinar will be a brief overview of the book with a question… Read More

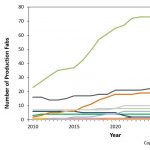

300mm Fab Watch 2019!

Unless you are new to SemiWiki you should be familiar with Scotten Jones, founder of IC Knowledge, semiconductor process expert, and blogger extraordinaire. Scott joined SemiWiki in 2014 and has been blogging ever since with 130 posted thus far.

Scott’s, company, IC Knowledge LLC, is the world leader in cost modeling of… Read More

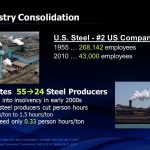

Chapter 5 – Consolidation of the Semiconductor Industry

For the last decade, semiconductor industry analysts have been writing articles and giving presentations that predict the increasing consolidation of the industry to the point where a few large companies dominate worldwide sales of semiconductor components. In recent years there has been some justification for this view… Read More

WEBINAR: The Brave New World of Customized Memory

The need to design low power devices is not new. However, the criticality of lowering the power consumption of chip designs has never been as important as it is now. In 1989, I purchased one of the first consumer cell phones produced by Panasonic. The battery was the size of a brick, but only about a third of the thickness. If the battery… Read More

Tortuga Webinar: Ensuring System Level Security Through HW/SW Verification

We all know (I hope) that security is important so we’re willing to invest time and money in this area but there are a couple of problems. First there’s no point in making your design secure if it’s not competitive and making it competitive is hard enough, so the great majority of resource and investment is going to go into that objective.… Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry