We have learned from nature that two characteristics are helpful for success, diversity and adaptability. The same has been shown to be true for computing systems. Things have come a long way from when CPU centric computing was the only choice. Much heavy lifting these days is done by GPUs, ASICs, and FPGAs, with CPUs in a support … Read More

Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More

Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More

Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More Alchip’s Leadership in ASIC Innovation: Advancing Toward 2nm Semiconductor TechnologyAlchip Technologies has recently reported significant progress in…Read More

Alchip’s Leadership in ASIC Innovation: Advancing Toward 2nm Semiconductor TechnologyAlchip Technologies has recently reported significant progress in…Read More CapEx Up for Foundry, MemorySemiconductor Intelligence estimates total semiconductor industry capital spending…Read More

CapEx Up for Foundry, MemorySemiconductor Intelligence estimates total semiconductor industry capital spending…Read MoreRwanda is Building Africa’s Very Own Silicon Valley – Known as Kigali Innovation City (KIC)

A multi-billion dollar project inspired by America’s Silicon Valley for the production and development of technological advancement is being built in Rwanda’s capital, Kigali.

This is an innovative effort, the first of its kind on the continent. The aim is to build a critical mass of talent, research and innovative… Read More

Intersection of Technologies

Monitoring brain activities and translating the signals into commands to control devices is truly a ‘Cool Idea’. Nurio is the latest winner of Protolabs’ Cool Idea award – a $250k grant towards manufacturing services to rapid prototype and accelerate the product to the market. (Click here to learn

Arm Inches Closer to Supercomputing

When it comes to Arm, we think mostly of phones and the “things” in the IoT. We know they’re in a lot of other places too, such as communications infrastructure but that’s a kind of diffuse image – “yeah, they’re everywhere”. We like easy-to-understand targets: phones, IoT devices, we get those. More recently Arm started to talk about… Read More

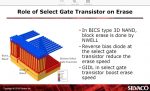

Webinar on coping with the complexities of 3D NAND design

In order to beat Moore’s Law NAND Flash memories have moved from a planar topology to 3D construction. This allows for increased memory sized in much the same way a multistory building provides more building square footage on the same size building lot. Just like in building construction, adding a third dimension to the mix increases… Read More

Why is Intel Still Short on Chips?

Intel is again apologizing to customers for 14nm chip shortages. As a result PC makers are revising down revenue expectations for 2020. Something does not smell right here. I have also read that due to the continued shortages Intel will be second sourcing CPU chips to Samsung 14nm. This smells even worse, absolutely.

First and foremost,… Read More

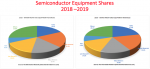

ASML Will Take Semiconductor Equipment Lead from Applied Materials in 2019

For the first time since 1990, Applied Materials is poised to lose its lead in the semiconductor equipment market, according to my recently published report “The Global Semiconductor Equipment: Markets, Market Shares, Market Forecasts.”

Applied Materials, which has been losing market share in the wafer front end (WFE) equipment… Read More

Intel vs AMD vs Google vs Amazon vs NUVIA

Arguably the cloud was the quickest road to riches for chip designers large and small. As an emerging company, if you wanted to raise money just put “Datacenter” in your pitch deck and you were assured millions. You would be competing with semiconductor’s version of David and Goliath (AMD and Intel) but that was a good thing, right?… Read More

Webinar Recap: IP Security Threats in your SoC

Three years ago my youngest son purchased a $17 smart watch on eBay, but then my oldest son read an article warning about how that watch would sync with your phone, then send all of your contact info to an address in China. My youngest son then wisely turned the watch off, and never used it again. Hackers have been able to spoof and hide … Read More

GM’s CES No Show: EmBARRAssing!

After failing in 2017 and 2018 to put a single woman on-stage to deliver a high profile keynote, the Consumer Technology Association featured four female keynoters in 2019. Until recently, two women were on the docket for the 2020 show in January, but news arrived last week that General Motors’ CEO Mary Barra had cancelled… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center