Artificial Intelligence (AI) and Machine Learning (ML) are becoming more and more commonplace in our world. We have Siri, Alexa and Google Assistant that understand our voice commands. Vision systems that recognize objects are used for facial recognition, autonomous driving, medical, geographical and many other applications.… Read More

Speculation: Silicon’s Most Expensive CompulsionHow Time-Based Scheduling Reclaims Silicon Wasted by Speculative…Read More

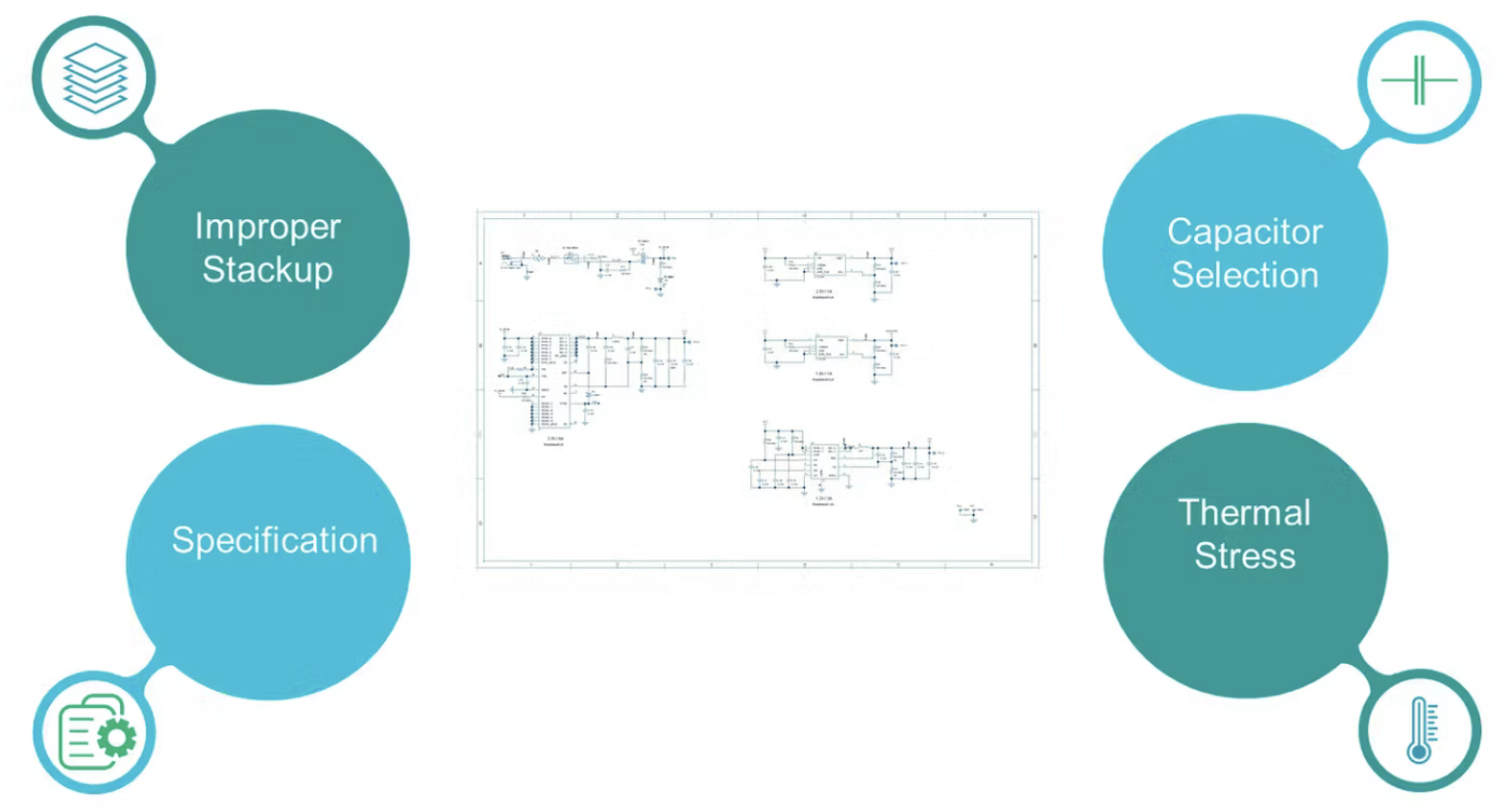

Speculation: Silicon’s Most Expensive CompulsionHow Time-Based Scheduling Reclaims Silicon Wasted by Speculative…Read More Exploring the Hidden Complexity of Modern Power Electronics Design – A Siemens White PaperReview the specifications of any state-of-the-art microcontroller and…Read More

Exploring the Hidden Complexity of Modern Power Electronics Design – A Siemens White PaperReview the specifications of any state-of-the-art microcontroller and…Read More Renesas Scalable Automotive SoC Design Using Arteris NoCThe increasing complexity of advanced driver assistance systems…Read More

Renesas Scalable Automotive SoC Design Using Arteris NoCThe increasing complexity of advanced driver assistance systems…Read MoreImec Technology Forum and ASML

On Thursday July 9 Imec held a virtual technology forum. Imec is one of the premier research organizations working on semiconductor technology and their forums are always interesting. My area of interest is process technology and the following are my observation in that area from the forum.

Luc Van Den Hove

Luc Van Den Hove is the… Read More

Designing AI Accelerators with Innovative FinFET and FD-SOI Solutions

I had the pleasure of spending time with Hiren Majmudar in preparation for the upcoming AI Accelerators webinar. As far as webinars go this will be one of the better ones we have done. Hiren has deep experience in both semiconductors and EDA during his lengthy career at Intel and now with a pure play foundry. He is intelligent, personable,… Read More

DAC Panel: Cadence Weighs in on AI for EDA, What Applications, Where’s the Data?

DAC was full of great panels, research papers and chip design stories this year, the same as other years. Being a virtual show, there were some differences of course. I’ve heard attendance was way up, allowing a lot more folks to experience the technical program. This is likely to be true for a virtual event. I’m sure we’ll see more… Read More

#57DAC – Panel Discussion of High Level Synthesis

Presenters took a trip down memory lane at DAC this year by having a panel discussion on HLS (High Level Synthesis) spanning from 1974 to 2020, and that time period aligns with when I first graduated from the University of Minnesota in 1978, starting chip design at Intel, then later transitioning into EDA companies by 1986. Marilyn… Read More

Low Power and RISC-V Talks at DAC2020, Hosted by Mentor

I’m going to get to low power and RISC-V, but first I’m trying out virtual DAC this year. Seems to be working smoothly, aside from some glitches in registration. But maybe that’s just me – I switched email addresses in the middle of the process. Some sessions are live, many pre-recorded, not quite the same interactive experience… Read More

A SoC Design Flow With IP-XACT

Taping out a SoC is never easy. The physical dimensions of the chip often belie the work which has been done to get to the tapeout stage. And it is still not a done deal as the hardware and software development teams await the arrival of the test chip from the foundry to complete the post silicon bring-up and validation. The pressure on… Read More

Synopsys Webinar: A Comprehensive Overview of High-Speed Data Center Communications

High-speed communication is a critical component for many applications, most notably in the data center. The serializer/deserializer physical interface, or SerDes PHY is the backbone of many different forms of high-speed communication for this application. Use cases include on chip, between chips, between boards and racks… Read More

VLSI Symposium 2020 – Imec Buried Power Rail

The 2020 VLSI Technology Symposium was held as a virtual conference from June 14th through June 19th. At the symposium Imec gave an interesting paper on Buried Power Rails (BPR) and I had a chance to interview one of the authors, Anshul Gupta.

As logic devices continue to scale down metal pitch is reaching a limit. Imec defines a pitch… Read More

The 10 Worst Cybersecurity Strategies

Counting down to the absolutely worst cybersecurity strategies. Sadly, these are all prevalent in the industry. Many organizations have failed spectacularly simply because they chose to follow a long-term path that leads to disaster. You know who you are…

Let’s count them down.

10. Cyber-Insurance

No need for security, … Read More

TSMC Technology Symposium 2026 Overview