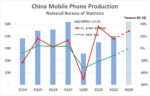

Data on China production of mobile phones from the National Bureau of Statistics of China indicates a double-digit decline in the year 2020. In 1Q 2020, the early stages of the COVID-19 pandemic, China mobile phone production declined 50% from 4Q 2019 and dropped 33% from a year earlier. Many factories were temporarily closed in… Read More

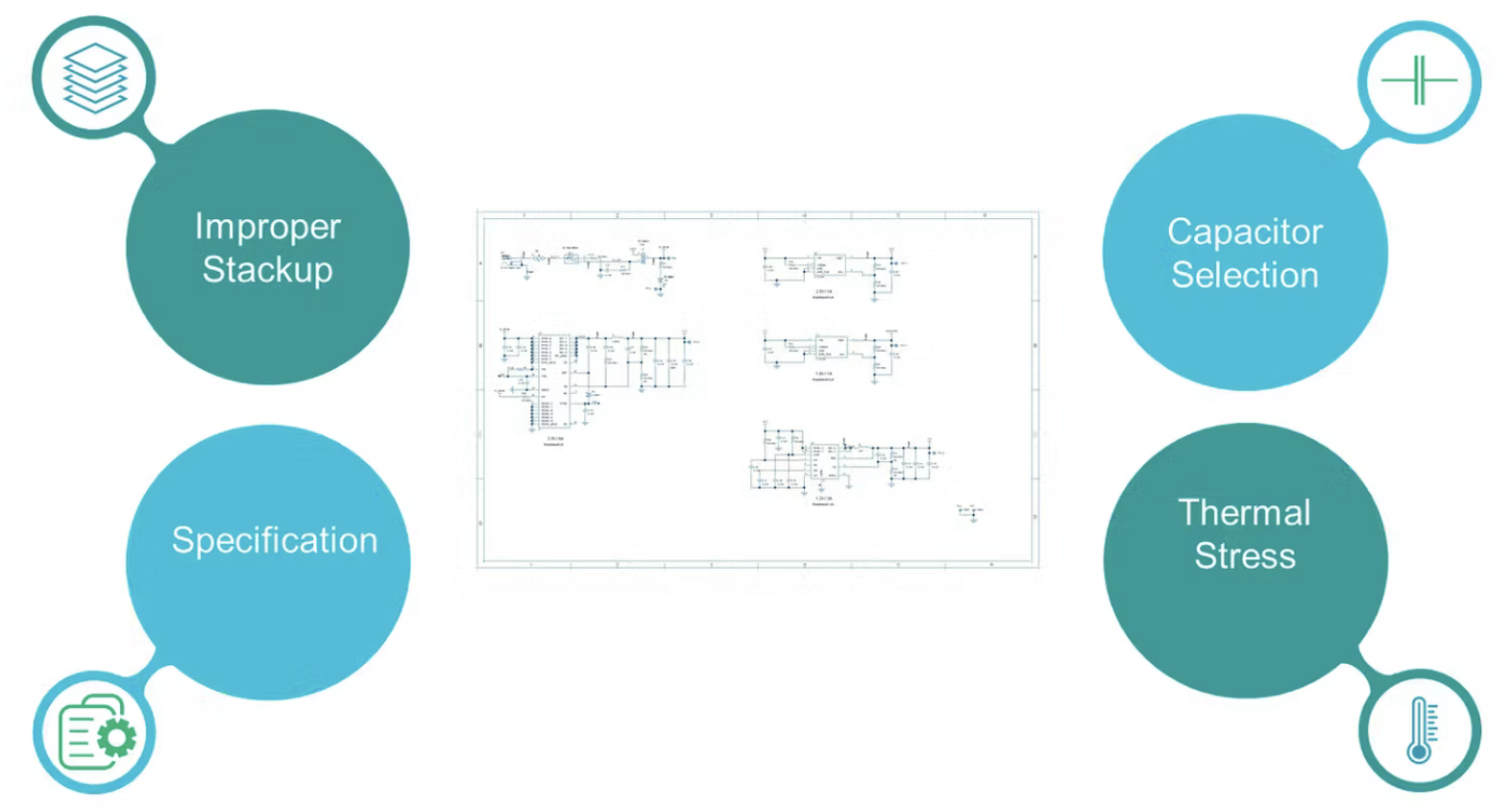

Exploring the Hidden Complexity of Modern Power Electronics Design – A Siemens White PaperReview the specifications of any state-of-the-art microcontroller and…Read More

Exploring the Hidden Complexity of Modern Power Electronics Design – A Siemens White PaperReview the specifications of any state-of-the-art microcontroller and…Read More Renesas Scalable Automotive SoC Design Using Arteris NoCThe increasing complexity of advanced driver assistance systems…Read More

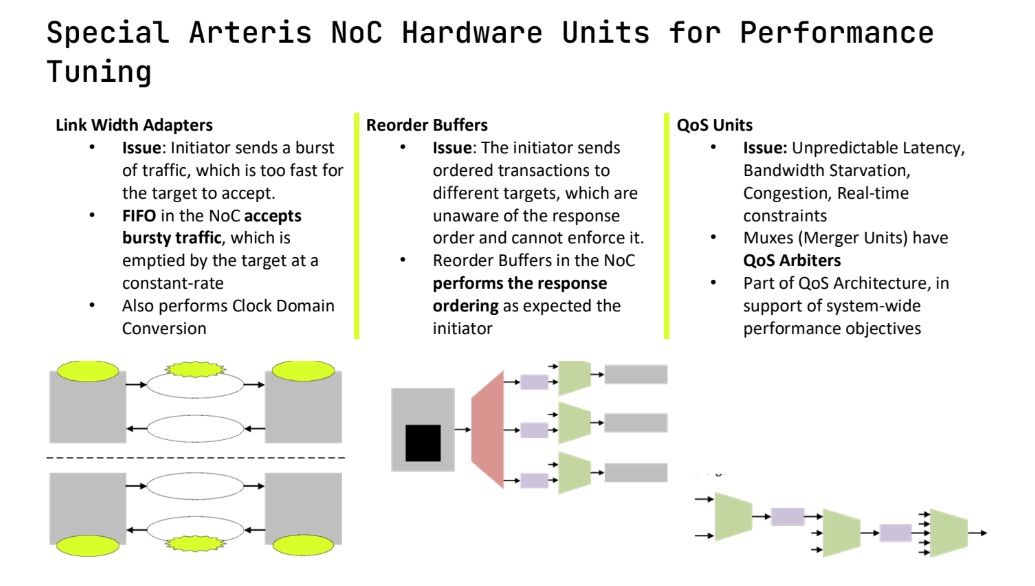

Renesas Scalable Automotive SoC Design Using Arteris NoCThe increasing complexity of advanced driver assistance systems…Read More Calibrating Quantum Computing Activity in Financial ServicesI was invited to listen in on an…Read More

Calibrating Quantum Computing Activity in Financial ServicesI was invited to listen in on an…Read More NoC Matters: Designing the Backbone of Next-Gen AI SoCsModern SoC design for artificial intelligence workloads has…Read More

NoC Matters: Designing the Backbone of Next-Gen AI SoCsModern SoC design for artificial intelligence workloads has…Read MoreSiemens is the True Catalyst for Secure and Trusted Digital Transformation

Introduction

For many years, I pondered the ultimate future of EDA. Companies such as Oracle, SAP and Dassault provide a huge array of enabling software infrastructure for the enterprise, including product design, mechanical design, project management and materials sourcing. But not for the all-important tasks of chip and… Read More

Arm Design Reviews add Mentor for Verification Review

Arm and Mentor Recently announced that the Arm Design Reviews program now offers Mentor help in verification design reviews. I talked to Paul Williams (Sr Consultant and Verification Practice Lead at Mentor Graphics) and Peter Lewin (Dir. Mktg at Arm Partner Enablement Group) to get more insight into Arm Design Services, particularly… Read More

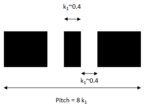

Impact of Defocus and Illumination on Imaging of Pitch

In an earlier article [1], the resolution limit for the space between paired features was described by the Rayleigh criterion of ~0.6 wavelength/numerical aperture, where the numerical aperture (NA) represented the sine of the largest angle for a ray focused from the lens to a point. It is also given by the radius of the lens divided… Read More

Synopsys Enhances Chips and Systems with New Silicon Lifecycle Management Platform

SLM. It’s a TLA (three-letter acronym) that you’ll be hearing more about. It stands for silicon lifecycle management and it has the potential of re-defining the role of EDA in the entire electronics ecosystem. A working definition of SLM is “monitoring, analysis and optimization of semiconductor devices as they are designed,… Read More

Cache Coherence Everywhere may be Easier Than you Think

I attended one of the Arm partner events in Cambridge many years ago, when they first talked about the coherent hub for managing cache coherence. I was impressed, but the obvious question even then was how any non-Arm IP was going to hook into this hub. They had a solution, of course, the ACE interface, and I left satisfied. As is the … Read More

Clarity 3D Transient Solver Speeds Up EMI/EMC Certification

Cadence made waves a while back with its innovative Clarity 3D Solver, a FEM solver for near field EM analysis. Now they are shaking things up with their new far field Clarity 3D Transient Solver. System level EMI and EMC analysis has often exceeded the limits of simulation tools, leading to expensive and time-consuming prototype… Read More

Coronavirus Remains Good for Semiconductors but not China

- LCRX puts up a solid QTR and slightly soft guidance

- China Concerns weigh on future but COVID remains driver

- Memory spend could be better & help offset China

Solid September Quarter

Lam reported Non GAAP EPS of $5.67 versus $5.19 street and Revenues of $3.18B which was $70M better than street expectations. Lam obviously does … Read More

Intel TSMC Update!

Based on the Intel investor call yesterday here are some interesting comments Bob Swan made related to Intel outsourcing manufacturing and 7nm progress. Let’s start with the prepared statement:

Bob Swan: “Over the last couple of years, we have been focused on three critical priorities; improving our execution to strengthen … Read More

CEO Interview: Andreas Kuehlmann of Tortuga Logic

You may remember Andreas from his time at Synopsys, where he led the new Software Integrity Business Unit. He joined Tortuga Logic a couple of months ago to lead the company. Given his background in software security, I was eager to get a CEO interview. Andreas is a EE with background at IBM in the PowerPC and EDA. He directed Cadence… Read More

Disaggregating LLM Inference: Inside the SambaNova Intel Heterogeneous Compute Blueprint