As semiconductor designs for many popular products move into smaller process nodes, the need for effective and rapid design closure is increasing. The SOCs used for many consumer and industrial applications are moving to FinFET nodes from 16 to 7nm and with that comes greater challenges in obtaining design closure. einfochips,… Read More

Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More

Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More

Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More Alchip’s Leadership in ASIC Innovation: Advancing Toward 2nm Semiconductor TechnologyAlchip Technologies has recently reported significant progress in…Read More

Alchip’s Leadership in ASIC Innovation: Advancing Toward 2nm Semiconductor TechnologyAlchip Technologies has recently reported significant progress in…Read More CapEx Up for Foundry, MemorySemiconductor Intelligence estimates total semiconductor industry capital spending…Read More

CapEx Up for Foundry, MemorySemiconductor Intelligence estimates total semiconductor industry capital spending…Read MoreAnalog Bits is Supplying Analog Foundation IP on the Industry’s Most Advanced FinFET Processes

The industry recently concluded a series of technology events for the all the major foundries. Done as virtual events this year, each one provided a significant update on technology platforms, roadmaps and ecosystem partnerships. These events are quite valuable to chip design teams who need to be aware of the latest in process,… Read More

No Intel and Samsung are not passing TSMC

Seeking Alpha just published an article about Intel and Samsung passing TSMC for process leadership. The Intel part seems to be a theme with them, they have talked in the past about how Intel does bigger density improvements with each generation than the foundries but forget that the foundries are doing 5 nodes in the time it takes… Read More

A Fast Checking Methodology for Power/Ground Shorts

The most vexing problem for physical implementation engineers is debugging errors due to power-ground “shorts”, as reported by the layout-versus-schematic (LVS) physical verification flow. The number of polygons associated with each individual grid is large – an erroneous connection between grids results in a huge number… Read More

Noose tightens on SMIC- Dead Fab Walking?

-US Administration to “blacklist” SMIC- Cutting off ALL US help

-A slow death versus a quick death (unlike Jinhua)

-There is enough time on way out door to leave scorched earth

-Reports in the Media about SMIC being “Blacklisted”

It has been widely reported that SMIC will be added to the US “Blacklist”… Read More

PLDA Brings Flexible Support for Compute Express Link (CXL) to SoC and FPGA Designers

A few months ago, I posted a piece about PLDA expanding its support for two emerging protocol standards: CXL™ and Gen-Z™. The Compute Express Link (CXL) specification defines a set of three protocols that run on top of the PCIe PHY layer. The current revision of the CXL (2.0) specification runs with the PCIe 5.0 PHY layer at a maximum… Read More

ML plus formal for analog. Innovation in Verification

Can machine learning be combined with formal to find rare failures in analog designs? ML plus formal for analog – neat! Paul Cunningham (GM, Verification at Cadence), Jim Hogan and I continue our series on research ideas. Here an idea from analog simulation sampling. Feel free to comment.

The Innovation

This month’s pick… Read More

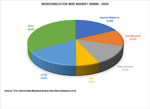

Applied Materials Will Regain Semiconductor Equipment Lead From ASML in 2020

On December 2, 2019, I posted a SemiWiki article entitled “ASML Will Take Semiconductor Equipment Lead from Applied Materials in 2019.”Since losing its dominance for the first time since 1990 in 2019, Applied Materials is poised to lose its retake the 2020 lead in the semiconductor equipment market. ASML led the… Read More

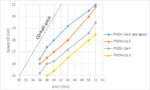

CD-Pitch Combinations Disfavored by EUV Stochastics

Ongoing investigations of EUV stochastics [1-3] have allowed us to map combinations of critical dimension (CD) and pitch which are expected to pose a severe risk of stochastic defects impacting the use of EUV lithography. Figure 1 shows a typical set of contours of fixed PNOK (i.e., the probability of a feature being Not OK due… Read More

Webinar: 5 Reasons Why Others are Adopting Hybrid Cloud and EDA Should Too!

With the complexity of transistors at an all time high and growing foundry rule decks, fabless companies consistently find themselves in a game of catch up. Semiconductor designs require additional compute resources to maintain speed and quality of development. But deploying new infrastructures at this current speed is a tall… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center