Uber, Lyft, Postmates, Instacart and Doordash were successful in their nearly $200M effort to pass California’s Proposition 22 in November – to allow gig operators to avoid treating their drivers as full-time employees with all of the associated employee benefits and legal protections. In the midst of a devastating pandemic… Read More

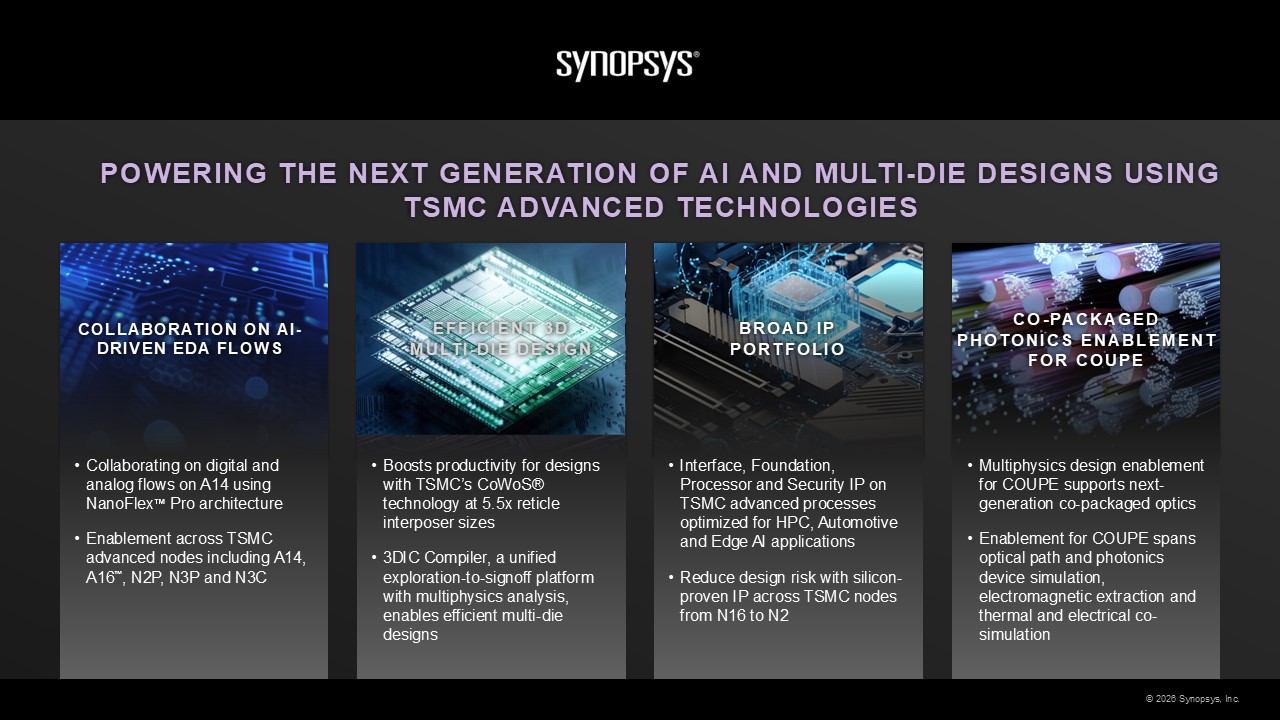

Synopsys and TSMC Deepen AI Design Alliance: What It MeansA recent announcement from Synopsys signals a meaningful…Read More

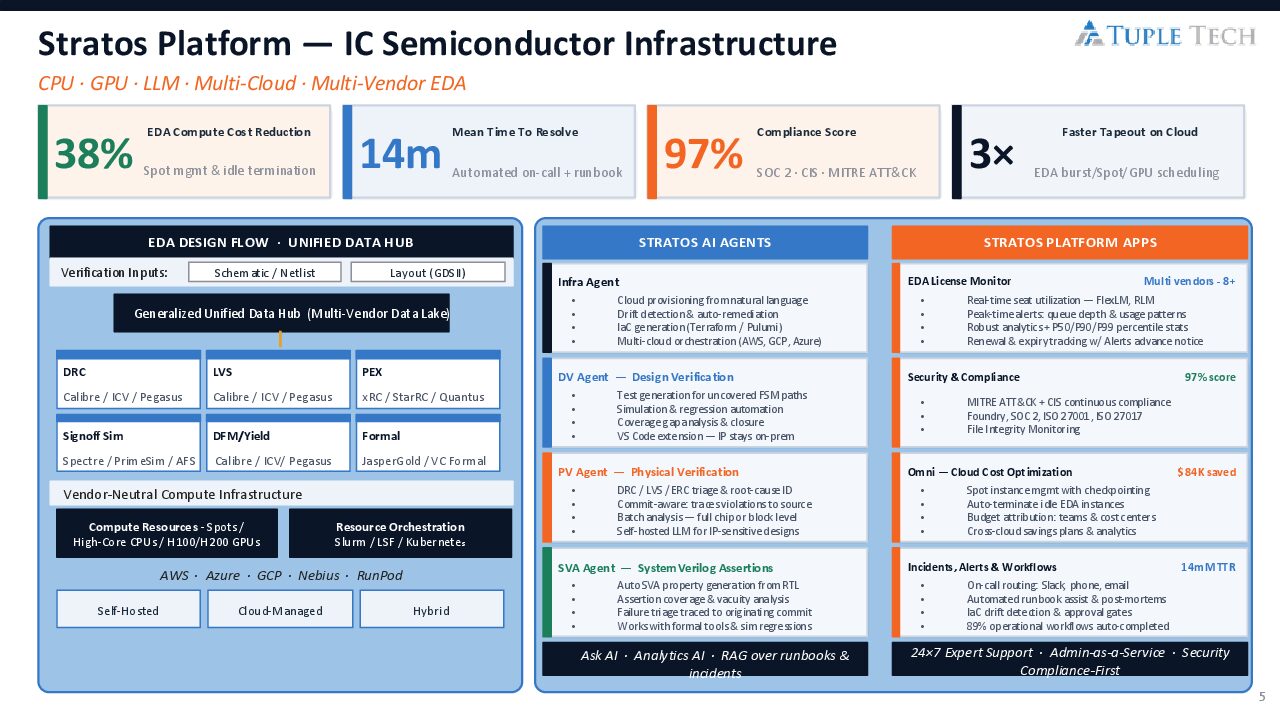

Synopsys and TSMC Deepen AI Design Alliance: What It MeansA recent announcement from Synopsys signals a meaningful…Read More Rethinking ECAD IT Infrastructure: From Fragmentation to an Engineering PlatformThe semiconductor industry is entering a new phase…Read More

Rethinking ECAD IT Infrastructure: From Fragmentation to an Engineering PlatformThe semiconductor industry is entering a new phase…Read MoreCES 2021 Goes All Digital

CES, the massive consumer technology show put on by the Consumer Technology Association (CTA), was held this week. Due to the global COVID-19 pandemic, CES 2021 was all digital. Last year, CES 2020 had over 170,000 attendees from over 160 countries and 4,400 exhibiting companies.

CES 2020 was held January 7-10, 2020 in Las Vegas,… Read More

CES 2021 and all things Cycling Technology

It’s January so time to give you another summary of what I’ve found at CES 2021 about new cycling products that have electronic content. During the pandemic in 2020 we’ve seen a surge in sales for bicycles, e-bikes, spin bikes and trainers as people wanted a simple way of getting around town running errands, or… Read More

Podcast EP3: Tomorrow’s Semiconductors with Jim Hogan

Dan and Mike are joined by industry luminary Jim Hogan. In a rare interview, Jim talks about his life – how he got into semiconductors, EDA and venture investing. Jim’s time at Cadence as well as his work at ARM are explored. Jim also provides a concise and informative overview of how venture investing works. The podcast… Read More

CEO Interview: Arun Iyengar of Untether AI

I had a chance to catch up with Arun Iyengar, CEO of Untether AI. Untether AI recently unveiled its tsunAImi accelerator cards powered by the company’s runAI devices. Using at-memory computation, Untether AI breaks through the barriers of traditional von Neumann architectures, offering industry-leading compute density … Read More

ISS 2021 – Scotten W. Jones – Logic Leadership in the PPAC era

I was asked to give a talk at the 2021 ISS conference and the following is a write up of the talk.

The title of the talk is “Logic Leadership in the PPAC era”.

The talk is broken up into three main sections:

- Background information explaining PPAC and Standard Cells.

- A node-by-node comparisons of companies running leading edge logic

HFSS – A History of Electromagnetic Simulation Innovation

In the 155 years since James Clerk Maxwell introduced the world to Maxwell’s Equations in the “Dynamic Theory of the Electromagnetic Field” there have been some amazing breakthroughs and avenues of insight. As a young electrical engineering student, we are introduced to the set of equations describing electromagnetic waves,… Read More

Developing Drivers For The Automotive Industry

Autonomous driving, connected vehicles, power electronics, infotainment and shared mobility are some of the developments which have mobilized the revolution within the automotive industry in recent years. Combined, they are not only disrupting the automotive value chain and impacting all stakeholders involved but are … Read More

2020 was a Mess for Intel

Understanding Intel’s future means understanding Intel’s past

Yes, there are two paths you can go by, but in the long run. There’s still time to change the road you’re on.

Intel is at a crossroad. The road they have been on since inception, and the road that has differentiated them from the rest of the pack… Read More

CDC, Low Power Verification. Mentor and Cypress Perspective

Clock domain crossing (CDC) analysis is unavoidable in any modern SoC design and is challenging enough to verify in its own right. CDC plus low power management adds more excitement to your verification task. I wrote on this topic for another solution provider last year. This time I want to intro an interesting twist on the problem,… Read More

Siemens U2U 3D IC Design and Verification Panel