I recently had a discussion with Tom Fitzpatrick of Siemens and Faris Khundakjie of Intel on the latest release of the Portable Test and Stimulus Standard (PSS). Faris chairs the PSS working group and Tom is vice-chair. In what follows I synthesize feedback from both, sometimes I call out interesting individual comments. My first… Read More

All in One Bluetooth Audio: A Complete Solution on a TSMC 12nm Single DieThe rapid evolution of wireless audio has placed…Read More

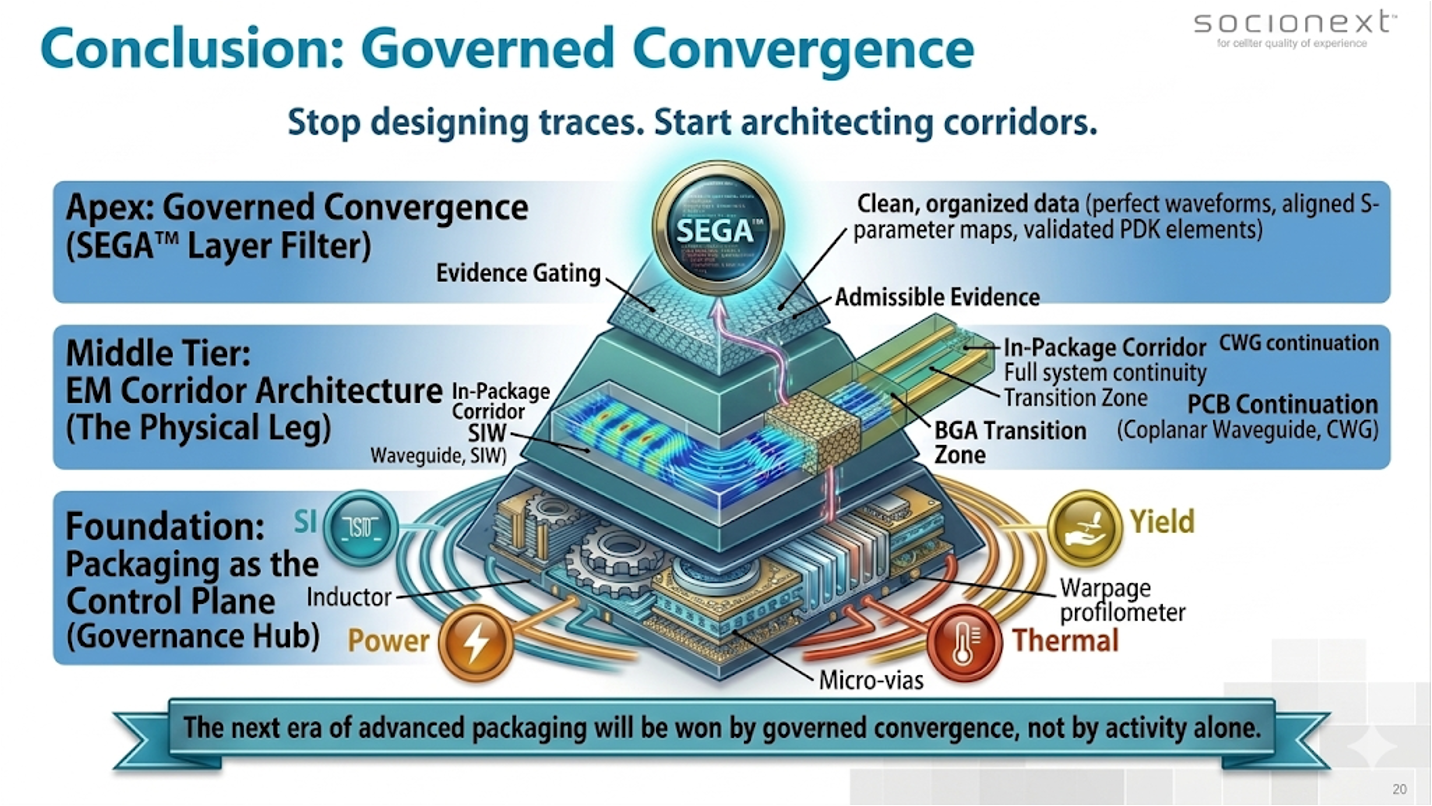

All in One Bluetooth Audio: A Complete Solution on a TSMC 12nm Single DieThe rapid evolution of wireless audio has placed…Read More Closing the Reality Gap: A New Architecture for 1.8-Tb/s Chiplet GovernanceBy Dr. Moh Kolbehdari Dr. Moh Kolbehdari is…Read More

Closing the Reality Gap: A New Architecture for 1.8-Tb/s Chiplet GovernanceBy Dr. Moh Kolbehdari Dr. Moh Kolbehdari is…Read More SemiWiki Q&A with Julie Rogers, Executive Director, ESD AllianceThe Electronic System Design Alliance (ESD Alliance), a SEMI…Read More

SemiWiki Q&A with Julie Rogers, Executive Director, ESD AllianceThe Electronic System Design Alliance (ESD Alliance), a SEMI…Read MoreFunctional Safety – What and How

I’ve written before about how the automotive industry adheres to functional safety (FS) as defined in the ISO 26262 standard, along with other SemiWiki bloggers. That standard certainly defines the What part of FS, however it doesn’t mandate how you meet the standard, what tools you should be using, file formats … Read More

Fuzzing to Validate SoC Security. Innovation in Verification

Fuzzing is to software verification what randomization is hardware verification. Can a fuzzing approach improve hardware security testing? Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO) and I continue our series on research ideas. As always, feedback… Read More

Molecular Sensing for Semiconductor Etch Applications

As process technologies have advanced, the difficulties in performing etch operations have increased. New structures and chemistries have created challenges in monitoring these complex operations. For instance, 3D-NAND structures call for high aspect ratio (HAR) trench etching. Likewise, in addition to involving Al, … Read More

Machine Learning Applied to Increase Fab Yield

Machine learning applications have become pervasive and increasingly complex, from recommendation agents in online interactions to personal assistants for command response to (ultimately) autonomous vehicle control. Yet, an often overlooked facet of machine learning technology is the deployment in industrial process… Read More

Avery Levels Up, Starting with CXL

Let me acknowledge up front that Avery isn’t the most visible EDA company around. If you know of them, you probably know their X-propagation simulator. Widely respected and used, satisfying a specialized need. They have also been quietly building over the years a stable of VIPs and happy customers, with a special focus on VIPs for… Read More

Safety Architecture Verification, ISO 26262

I love to read articles about autonomous vehicles and the eventual goal of reaching level 5, Full Automation, mostly because of the daunting engineering challenges in achieving this feat and all of the technology used in the process. The auto industry already has a defined safety requirements standard called ISO 26262, and one… Read More

WEBINAR: What Makes SoC Compiler The Shortest Path from SoC Design Specification to Logic Synthesis?

Defacto SoC Compiler whose 9.0 release was announced recently automates the SoC design creation from the first project specifications. It covers register handling, IP and connectivity insertion at RTL, UPF and SDC file generation right to logic synthesis. As part of the generation process of RTL and design collaterals, basic… Read More

Supply Issues Limit 2021 Semiconductor Growth

Worldwide semiconductor shipments were $123.1 billion in 1Q 2021, up 3.6% from 4Q 2020 and up 17.8% from a year ago, according to WSTS. The 3.6% quarter-to-quarter growth was the highest for a first quarter since 1Q 2010, eleven years ago. The strong growth in 1Q21 implies strong growth in the following quarters and for the year 2021.… Read More

AMAT Nice Beat Strong Growth for Both 2021 & 2022

-Strong beat & guide- WFE up in 2021 & 2022-$160B combined

-Taking share in conductor etch & CVD

-Traditional Moore Scaling – No More?

-Foundry Logic leads followed by DRAM with weak NAND

Nice beat & guide & raise

Applied reported revenues of $5.58B with GM of 47.5% resulting in non-GAAP EPS of $1.63. … Read More

Is Intel About to Take Flight?