-The semiconductor industry is not to blame its the customers

-How do you fix something that’s not really broken?

-Long taken for granted, semi’s are sexy again

-Pawns in a Political Power Play?

Its not the chip makers that screwed up. It’s the customers that stressed the system beyond breaking

The semiconductor… Read More

Mad scientists have been a staple of Hollywood science fiction since Dr Victor Frankenstein created his eponymous monster in 1931. Pre-pandemic, the Marvel Cinematic Universe was the main source of on-screen geeks-turned-superheroes, from Iron Man’s Tony Stark to Ant Man’s Hank Pym.

When it comes to real-life scientists on… Read More

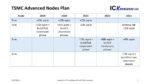

TSMC recently announced plans to spend $100 billion dollars over three years on capital. For 2021 they announced $30B in total capital with 80% on advanced nodes (7nm and smaller), 10% on packaging and masks and 10% on “specialty”.

If we take a guess at the capital for each year, we can project something like $30B for 2021 (announced),… Read More

Dan and Mike are joined by semiconductor and EDA executive Jack Harding. Jack has a diverse career as a technology executive beginning at IBM with notable stops along the way, including taking Cooper and Chyan Technology public, taking the helm from Joe Costello as CEO of Cadence and most recently as the founding CEO of eSilicon,… Read More

Automakers worldwide have scaled back production due to a shortage of semiconductors. Companies which have announced temporary halts on production include Volkswagen, Toyota, General Motors, Ford, Nissan, Honda, Suzuki, Mitsubishi, Daimler (Mercedes) and Stellantis (merger of Fiat-Chrysler and Peugot).

IHS Markit estimates… Read More

Dr. Shen has been President of eMemory Technology since 2009, succeeding Dr. Charles Hsu. Prior to the appointment, Dr. Shen held various management positions within the company, overseeing Technology Development, founding the Customer Service team, supervising Technology & IP services, and the company’s technology… Read More

In early April, Gabriele Saucier kicked off Design & Reuse’s IPSoC Silicon Valley 2021 Conference. IPSoC conference as the name suggests is dedicated to semiconductor intellectual property (IP) and IP-based electronic systems. There were a number of excellent presentations at the conference. The presentations had been… Read More

SoC integration offers huge benefits through reduced chip count in finished systems, higher performance, improved reliability, etc. A single die can contain billions of transistors, with multiple processors and countless subsystems all working together. The result of this has been rapid growth of semiconductor content … Read More

A vexing chip design issue is how to achieve (or improve) performance and power dissipation targets, allowing for a wide range of manufacturing process variation (P) and dynamic operation voltage and temperature fluctuations (VT). One design method is to analyze the operation across a set of PVT corners, and ensure sufficient… Read More

This wasn’t as much of a big bang announcement as others I have seen. More a polishing of earlier-announced reveals, positioning updates, together with some new concepts. First, you probably remember the Cortex-X announcement from about a year ago, allowing users to customize their own instructions into the standard instruction… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era