At the recent RISC-V Now event hosted by Andes, the discussion underscored the fact that RISC-V is no longer just about instruction set architecture advantages or customizable cores. The real focus has moved up the stack to system-level design. This is where connectivity, integration, and security define whether an innovation… Read More

CEO Interview with Dave Kelf, CEO of Breker Verification SystemsIn the functional verification space, Breker Verification Systems stands…Read More

CEO Interview with Dave Kelf, CEO of Breker Verification SystemsIn the functional verification space, Breker Verification Systems stands…Read More RISC-V: From Niche Architecture to Strategic FoundationAt the recent RISC-V Now by Andes conference,…Read More

RISC-V: From Niche Architecture to Strategic FoundationAt the recent RISC-V Now by Andes conference,…Read More Bringing mathematical rigour in the world of hardware - a journey into Formal VerificationThis interview presents the first steps of Robert…Read More

Bringing mathematical rigour in the world of hardware - a journey into Formal VerificationThis interview presents the first steps of Robert…Read More The Great Divide: A Tale of Three Hardware Emulation ArchitecturesHardware emulation arose as a necessity out of…Read More

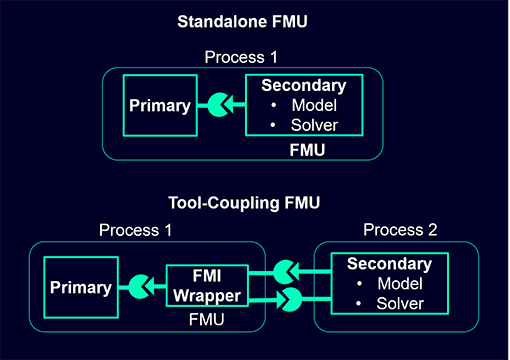

The Great Divide: A Tale of Three Hardware Emulation ArchitecturesHardware emulation arose as a necessity out of…Read More A Different Angle on Co-Simulation for SystemsCo-simulation, two or more simulations running concurrently in…Read More

A Different Angle on Co-Simulation for SystemsCo-simulation, two or more simulations running concurrently in…Read MoreRethinking ECAD IT Infrastructure: From Fragmentation to an Engineering Platform

The semiconductor industry is entering a new phase of complexity. Advanced nodes, heterogeneous integration, and AI-driven design workflows are placing unprecedented demands on engineering teams. While much of the focus remains on tools and methodologies, an equally critical constraint is emerging beneath the surface:… Read More

CEO Interview with Geoffrey Rodgers of Chameleon Semiconductor

Geoffrey Rodgers spent most of his career at the intersection of semiconductor technology and go-to-market execution, with a focus on scaling businesses and bringing complex solutions to market. He previously led the Analog Go-To-Market motion at Synopsys following the acquisition of Analog Design Automation and held leadership… Read More

Bronco AI Webinar: Full-Chip SoC Debug in 15 Minutes

A single bug on a full-chip SoC can pull engineers off roadmap work for days or even weeks. It involves massive waveforms, thousands of files of RTL and UVM, and dense specs that aren’t always perfect. Finding these bugs have always been a matter of engineer-hours and how well knowledge diffuses through the organization.

Bronco … Read More

Podcast EP344: An Overview of the Upcoming Sensors Converge Event with David Drain

Daniel is joined by David Drain, show director for Questex’s Sensors Converge and Broadband Nation Expo, where he leads strategy, content, and industry engagement for two of the company’s flagship technology events. Prior to joining Questex, David spent more than 15 years with Networld Media Group, most recently as senior vice… Read More

Dr. L.C. Lu on TSMC Advanced Technology Design Solutions

L.C. leads efforts in design enablement, ensuring that the company can meet the diverse and evolving requirements of its global customer base. Prior to this, he headed the Design and Technology Platform organization starting in 2018.

Since joining TSMC in 2000, Dr. Lu has held multiple leadership positions in design services.… Read More

Solving the EDA tool fragmentation crisis

By Samar Abd El-Hady and Wael ElManhawy

Design teams today face an uncomfortable truth: the specialized tools they need to verify modern ICs can’t reliably share the same design data. As geometries shrink below five nanometers and designs incorporate billions of transistors across multiple dies, no single Electronic… Read More

Dr. Y.J. Mii on TSMC Technology Leadership in 2026

Dr. Y.J. Mii joined TSMC in 1994 as a manager at Fab 3 before moving into the company’s research and development organization in 2001. He was appointed Vice President of R&D in 2011 and later advanced to Senior Vice President in November 2016.

Over more than 20 years at TSMC, Dr. Mii has played a central role in advancing and manufacturing… Read More

Advanced Microelectronics Paving the Way for 6G with Alphacore

The world stands at the threshold of a new era in wireless communication as research communities, standards bodies, and technology companies begin shaping what will become sixth generation mobile networks. While fifth generation systems are still expanding across global markets, attention has already shifted toward defining… Read More

Enabling Next-Generation AI Through Advanced Packaging and 3D Fabric Integration

The rapid rise of artificial intelligence is fundamentally reshaping computing architectures. As AI models scale toward trillions of parameters, traditional approaches to performance improvement are no longer sufficient. Instead, the industry is entering a new era where system-level innovation, advanced packaging, … Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!