Digital IC design gets a lot of attention, because all of our modern devices primarily use digital logic, but in reality whenever you have a sensor like a camera, accelerometer, gyroscope or any radio like Bluetooth, WiFi or NFC, then you’re really in the realm of analog, and that’s where mixed-signal IC design comes… Read More

UX in Agentic Systems. Innovation in VerificationA switch this month to principles behind building…Read More

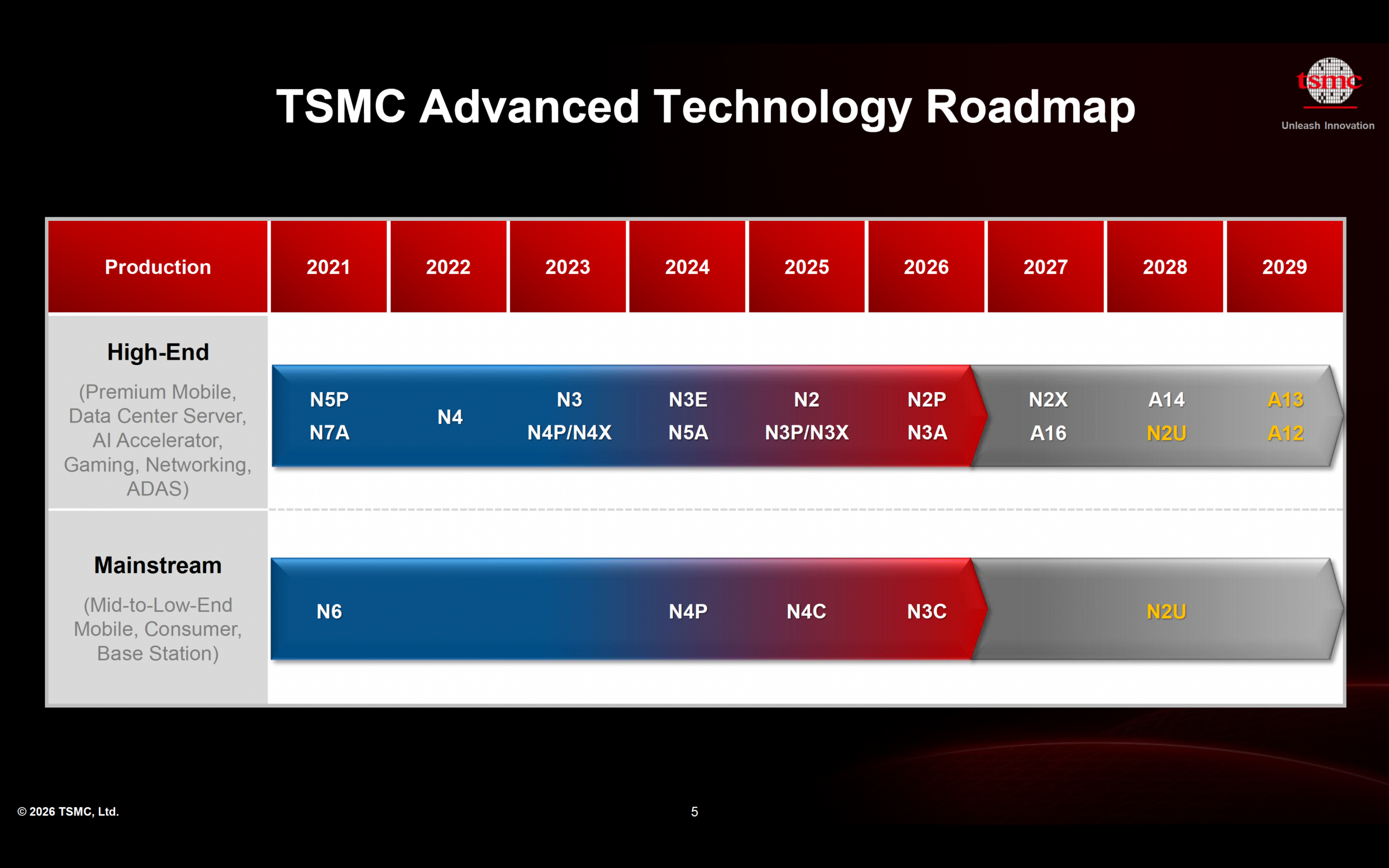

UX in Agentic Systems. Innovation in VerificationA switch this month to principles behind building…Read More The Shift to System-Level AI Drives Next-Generation SiliconAt its 2026 Technology Symposium, TSMC delivered a…Read More

The Shift to System-Level AI Drives Next-Generation SiliconAt its 2026 Technology Symposium, TSMC delivered a…Read More All in One Bluetooth Audio: A Complete Solution on a TSMC 12nm Single DieThe rapid evolution of wireless audio has placed…Read More

All in One Bluetooth Audio: A Complete Solution on a TSMC 12nm Single DieThe rapid evolution of wireless audio has placed…Read MoreSmoothing the Path to NoC Adoption

We’re creatures of habit. As technologists, we want to move fast and break things, but only on our terms. Everything else should remain the same or improve with minimum disruption. No fair breaking the way we do our jobs as we plot a path to greatness. This is irrational, of course. Real progress often demands essential changes where… Read More

Webinar – Why Keeping Track of IP in the Enterprise Really Matters

Everyone knows IP is an important asset for the enterprise. You spend a lot of money on IP licenses. You try to keep track of who bought what as buying the same thing twice is painful. You wonder if you have the latest version of an IP, especially if it’s part of mission-critical functionality. If you’re a good corporate citizen, you … Read More

NetApp’s ONTAP Enables Engineering Productivity Boost

One of the few things that remain constant in the engineering world is the desire for higher productivity. Innovation happens when engineers are designing something and creative ideas crop up when they are reviewing and analyzing the results. In between these fun steps, engineers have to deal with the necessary evil of creating… Read More

GM Fires First 5G Shot

Connecting cars remains one of the most unnatural acts in the world of IoT. “Connected Car” headlines might make you think otherwise, but the reality is that precious few cars on the road today are connected with a live, provisioned and functioning wireless connection. That being said, General Motors claims 16M of those cars

Accelerating Exhaustive and Complete Verification of RISC-V Processors

As processor architecture and design development becomes completely liberated with open-source RISC-V instruction set architecture (ISA), the race to get RISC-V silicon in our hands has increased massively. We have no doubt that in next 5 years, we will see RISC-V based laptops and desktops in the market. But would these processors… Read More

Podcast EP35: Benefits of FPGA Based Prototyping

Dan is joined by Ying Chen, VP of marketing & international sales at S2C. Dan and Ying explore the various uses and benefits of FPGA-based prototyping, including the different architectures available and cloud access.

Mr. Chen is a dynamic technologist with over 23 years of technical and business experiences in digital … Read More

CEO Interview: Veerbhan Kheterpal of Quadric.io

It was my pleasure to meet Veerbhan Kheterpal. Veerbhan has founded three technology companies and has full stack expertise spanning software to silicon across Edge & Datacenter applications. Currently, he is a CEO & co-founder of quadric.io, a company that has created a new processor architecture for high performance… Read More

Side Channel Analysis at RTL. Innovation in Verification

Roots of trust can’t prevent attacks through side-channels which monitor total power consumption or execution timing. Correcting weakness to such attacks requires pre-silicon vulnerability analysis. Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO)… Read More

Using Machine Learning to Improve EDA Tool Flow Results

Back in 2020 I first learned from Synopsys about how they had engineered a better way to do optimize layouts on digital designs by using machine learning techniques, instead of relying upon manual approaches. The product was named DSO.ai, standing for Design Space Optimization, and it produced a more optimal floor-plan in less… Read More

Solving the EDA tool fragmentation crisis