Analog Bits, the industry’s leading provider of low-power mixed-signal IP solutions will be demonstrating several IP’s in TSMC advanced nodes at DAC. Analog Bits is also a long time DAC supporter and very active in the semiconductor and on SemiWiki, absolutely. Great company!

As power management and energy efficiency is getting… Read More

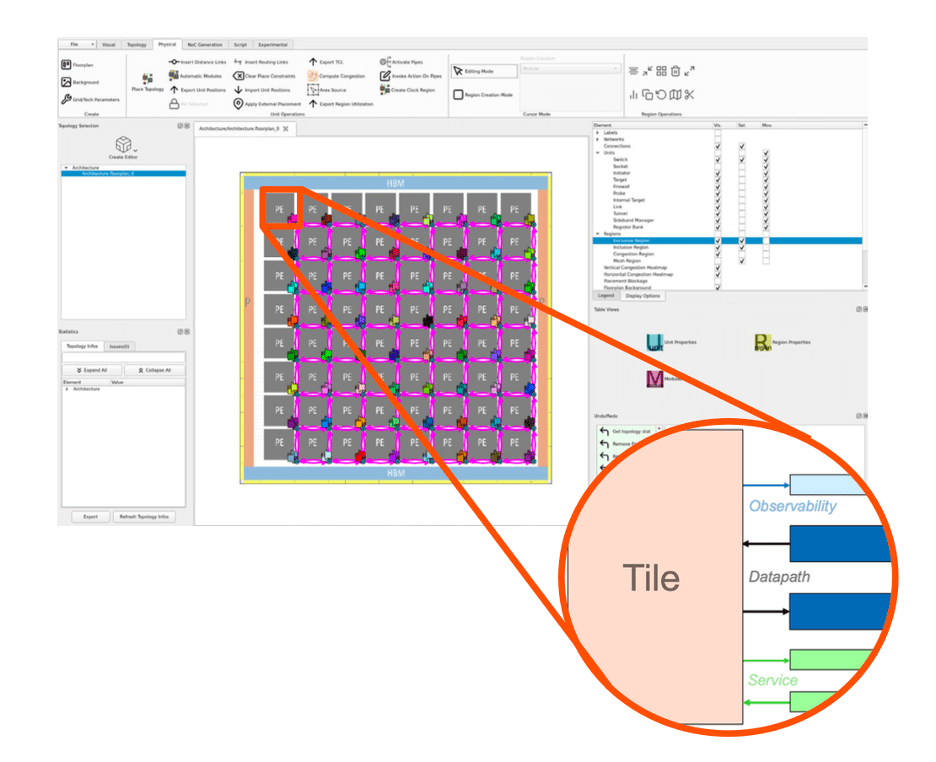

Build a 100% Python-based Design environment for Large SoC Designs