In a few short years, self-driving tech enfant terrible George Hotz managed to get a rebuff from Tesla CEO Elon Musk and a brush back from both the California Department of Motor Vehicles and the National Highway Traffic Safety Administration (NHTSA) while single-handedly inventing the aftermarket for autonomous vehicle technology. … Read More

When a Platform Provider Becomes a Competitor: Why Arm’s Silicon Strategy Changes the IncentivesMarc Evans, Director of Business Development & Marketing,…Read More

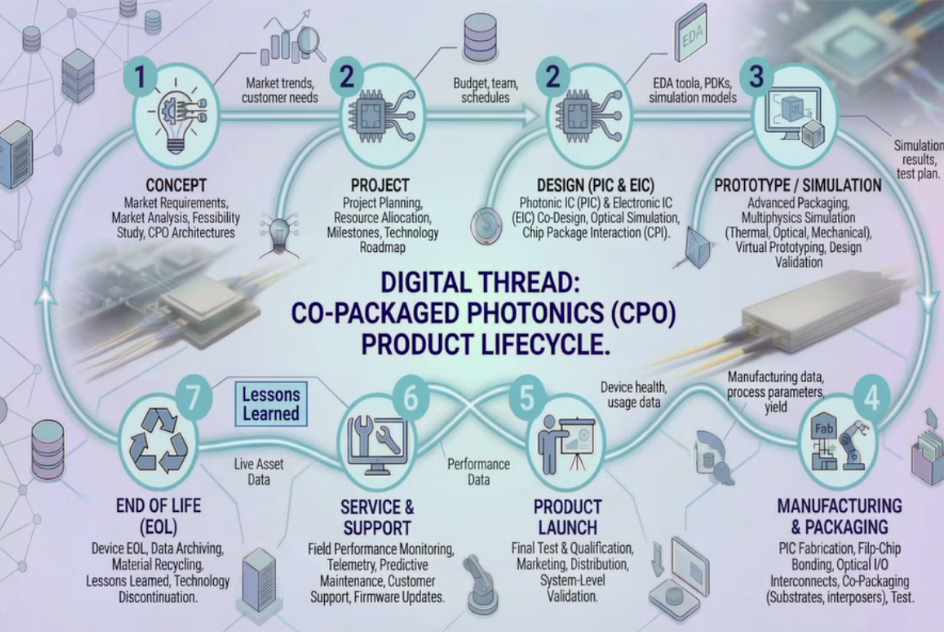

When a Platform Provider Becomes a Competitor: Why Arm’s Silicon Strategy Changes the IncentivesMarc Evans, Director of Business Development & Marketing,…Read More yieldWerx Delivers a Master Class in Co-Packaged Photonics ImplementationWe all know the semiconductor industry is seeing…Read More

yieldWerx Delivers a Master Class in Co-Packaged Photonics ImplementationWe all know the semiconductor industry is seeing…Read More RISC-V Has Momentum. The Real Question Is Who Can DeliverRISC-V has momentum. The industry knows it. The…Read More

RISC-V Has Momentum. The Real Question Is Who Can DeliverRISC-V has momentum. The industry knows it. The…Read More Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More

Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read MorePodcast EP121: Managing Design Flows and EDA Resources with Innova

Dan is joined by Chouki Aktouf, founder & CEO of Defacto Technologies and co-founder of Innova Advanced Technologies. Prior to founding Defacto in 2003, Dr. Aktouf was an associate professor of Computer Science at the University of Grenoble – France and leader of a dependability research group. He holds a PhD in Electric Engineering… Read More

Blockchain 4.0

The simple and best definition of Blockchain technology is to think about it as electricity , you only see it’s applications but you understand how important it’s and know there are many applications and products that can run on it . But like any other technology it went through stages and evolved as it progressed and matured. We started… Read More

Integrating High Speed IP at 5nm

Introduction:

The advancements in deep submicron technology and adding multiple functionalities to reduce costs combined with scaling existing operations means that SoC designs become ever more complex. The biggest driving factors to go below the 16nm process node are the decrease in power and the increase in performance … Read More

Podcast EP120: How NXP is Revolutionizing Automotive Electronics Design

Dan is joined by Jim Bridgewater, director of product marketing for NXP automotive edge product line.

Jim provides an overview of the various wireless interfaces in current automotive design. He also discusses a new product from NXP called OrangeBox, a device that combines many of these interfaces into one domain controller.… Read More

MIPI in the Car – Transport From Sensors to Compute

I’ve written on and off about sensors, ML inference of the output of those sensors and the application of both in modern cars. Neither ADAS nor autonomous/semi-autonomous driving would be possible without these. But until now I have never covered the transport between sensors and the compute that safely turns what they produce… Read More

SoC Design Closure Just Got Smarter

Near the end of any large SoC design project, the RTL code is nearly finished, floorplanning has been done, place and route has a first-pass, static timing has started, but the timing and power goals aren’t met. So, iteration loops continue on blocks and full-chip for weeks or even months. It could take a design team 5-7 days… Read More

Electron Blur Impact in EUV Resist Films from Interface Reflection

The resolution of EUV lithography is commonly expected to benefit from the shorter wavelengths (13.2-13.8 nm) but in actuality the printing process needs to include Pde the consideration of the lower energy electrons released by the absorption of EUV photons. The EUV photon energy itself has a nominal energy range of 90-94 eV,… Read More

Truechip Introduces Automation Products – NoC Verification and NoC Performance

While Truechip has established itself as a global provider of verification IP (VIP) solutions, they are always on the lookout for strategic IP needs from their customer base. Over the last several years, a solid market for Network-on-Chip (NoC) IP has grown, driven by the need to rapidly move data across a chip. Concurrently, the… Read More

Your Symmetric Layouts show Mismatches in SPICE Simulations. What’s going on?

This Diakopto paper discusses for the first time, a new effect – a false electrical mismatch in post-layout simulations for perfectly symmetric nets. This effect is caused by the difference in distributions of parasitic coupling capacitors over the nodes of parasitic resistor networks, even for symmetric nets. This, in turn,… Read More

Intel, Musk, and the Tweet That Launched a 1000 Ships on a Becalmed Sea