RF and microwave design is no longer confined to a few defense and aerospace EEs huddled in dark cubicles working with spreadsheets and primitive circuit simulators. Now, areas like 5G and automotive demand complex RF systems. Advanced RF and microwave EDA tools are taking on electromagnetic (EM), thermal, and power simulation,… Read More

#DAC2026 Marks Another Pivotal Moment for the Semiconductor IndustryThe 2026 Design Automation Conference (DAC 2026) marks…Read More

#DAC2026 Marks Another Pivotal Moment for the Semiconductor IndustryThe 2026 Design Automation Conference (DAC 2026) marks…Read More IPLM: Future Forward Webinar May 19thStep into the future of semiconductor design management…Read More

IPLM: Future Forward Webinar May 19thStep into the future of semiconductor design management…Read More From Point Solutions to Agentic AI Ecosystems: Semiconductor Process Control Depends on Its PastAgentic AI is often presented as a revolutionary…Read More

From Point Solutions to Agentic AI Ecosystems: Semiconductor Process Control Depends on Its PastAgentic AI is often presented as a revolutionary…Read More Panel Discission: Beyond Moore's Law and the Future of Semiconductor ManufacturingThe semiconductor industry is entering a post-Moore’s Law…Read More

Panel Discission: Beyond Moore's Law and the Future of Semiconductor ManufacturingThe semiconductor industry is entering a post-Moore’s Law…Read More CEO Interview with Dave Kelf, CEO of Breker Verification SystemsIn the functional verification space, Breker Verification Systems stands…Read More

CEO Interview with Dave Kelf, CEO of Breker Verification SystemsIn the functional verification space, Breker Verification Systems stands…Read MorePodcast EP143: FPGAs, eFPGAs and the Emerging Chiplet Market

Dan is joined by Nick Ilyadis, Senior Director of Product Planning at Achronix. With over 35 years of data and semiconductor engineering and manufacturing experience and 72 issued patents under his name, Nick is a recognized expert on software and hardware development and quality control.

Dan explores the emerging chiplet market… Read More

Dr. Anirudh Devgan Elected to The National Academy of Engineering (NAE)

Having known many of the top EDA CEOs during my semiconductor tenure the common traits I have found are brilliance, humility, endurance, and a sharp sense of humor. EDA solves so many problems, complex problem after complex problem, that it takes teams of incredibly smart people to solve them. Even more difficult is leading these… Read More

The State of IC and ASIC Functional Verification

Way back in 2002 there was a study from Collett International Research on functional verification, and since 2010 the Wilson Research Group has continued that same kind of study with a new report every two years. What attracts me to this report is that it doesn’t just look at the installed base of one EDA vendor, instead it looks… Read More

Synopsys Design Space Optimization Hits a Milestone

I talked recently with Stelios Diamantidis (Distinguished Architect, Head of Strategy, Autonomous Design Solutions) about Synopsys’ announcement on the 100th customer tapeout using their DSO.ai solution. My concern on AI-related articles is in avoiding the hype that surrounds AI in general, and conversely the skepticism… Read More

Cliosoft’s Smart Storage Strategy for Better Workspace Management

Over the years storage has gotten very cheap, or has it? As a typical consumer, we take data storage for granted because access to it has gotten very cheap. Long gone are the days of being limited to 1.44MB floppy disks to store data. The smart devices we carry around with us can store 100’s of GB of data. That is a lot of data. But what about… Read More

ASIL B Certification on an Industry-Class Root of Trust IP

I have always been curious about how Austemper-based safety methodologies (from Siemens EDA) compares with conventional safety flows. Siemens EDA together with Rambus recently released a white paper on getting a root of trust IP to ASIL B certification. This provides a revealing insight beyond the basics of fault simulation… Read More

3DIC Physical Verification, Siemens EDA and TSMC

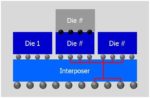

At SemiWiki we’ve written four times now about how TSMC is standardizing on a 3DIC physical flow with their approach called 3Dblox, so I watched a presentation from John Ferguson of Siemens EDA to see how their tool flow supports this with the Calibre tools. With a chiplet-based packaging flow there are new physical verification… Read More

Advances in Physical Verification and Thermal Modeling of 3DICs

If, like me, you’ve been paying too little attention to historically less glamorous areas of chip design like packaging, you’ll wake up one day and realize just how much things have changed and continue to advance and how interesting it’s become.

One of the main drivers here is the increasing use of chiplets to counter the decreasing… Read More

Privacy? What Privacy?

It seems as if every day brings news of yet another company that is using artificial intelligence to leverage smartphone data for “non-invasive” analytics of human movement. Our smartphones and smartwatches and fitbits can detect whatever activity we are doing, how well or poorly we are doing it, how it is affecting our mood, … Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!