AI, hyperscale data centers, and data-intensive workloads are driving unprecedented demands for performance, bandwidth, and energy efficiency. As the economic returns of traditional transistor scaling diminish, advanced IC packaging and heterogeneous integration have become the primary levers for system-level scaling.… Read More

proteanTecs at Chiplet Summit – Changing the Game for Health & Performance Monitoring of ChipletsThe recent Chiplet Summit 2026 was a great…Read More

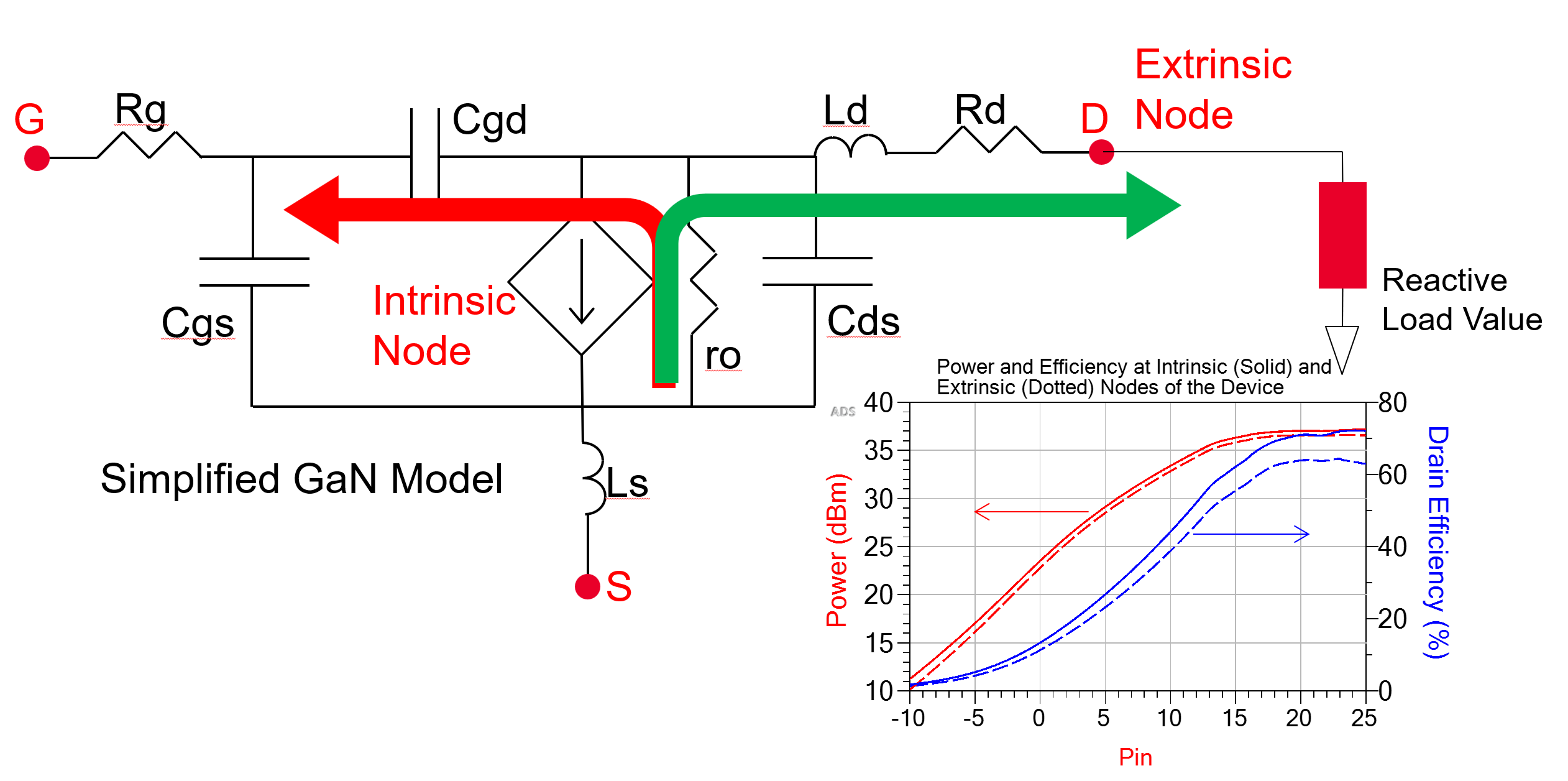

proteanTecs at Chiplet Summit – Changing the Game for Health & Performance Monitoring of ChipletsThe recent Chiplet Summit 2026 was a great…Read More WEBINAR: Intrinsic Techniques in RF Power Amplifier DesignLoad-pull power amplifier (PA) design techniques determine the…Read More

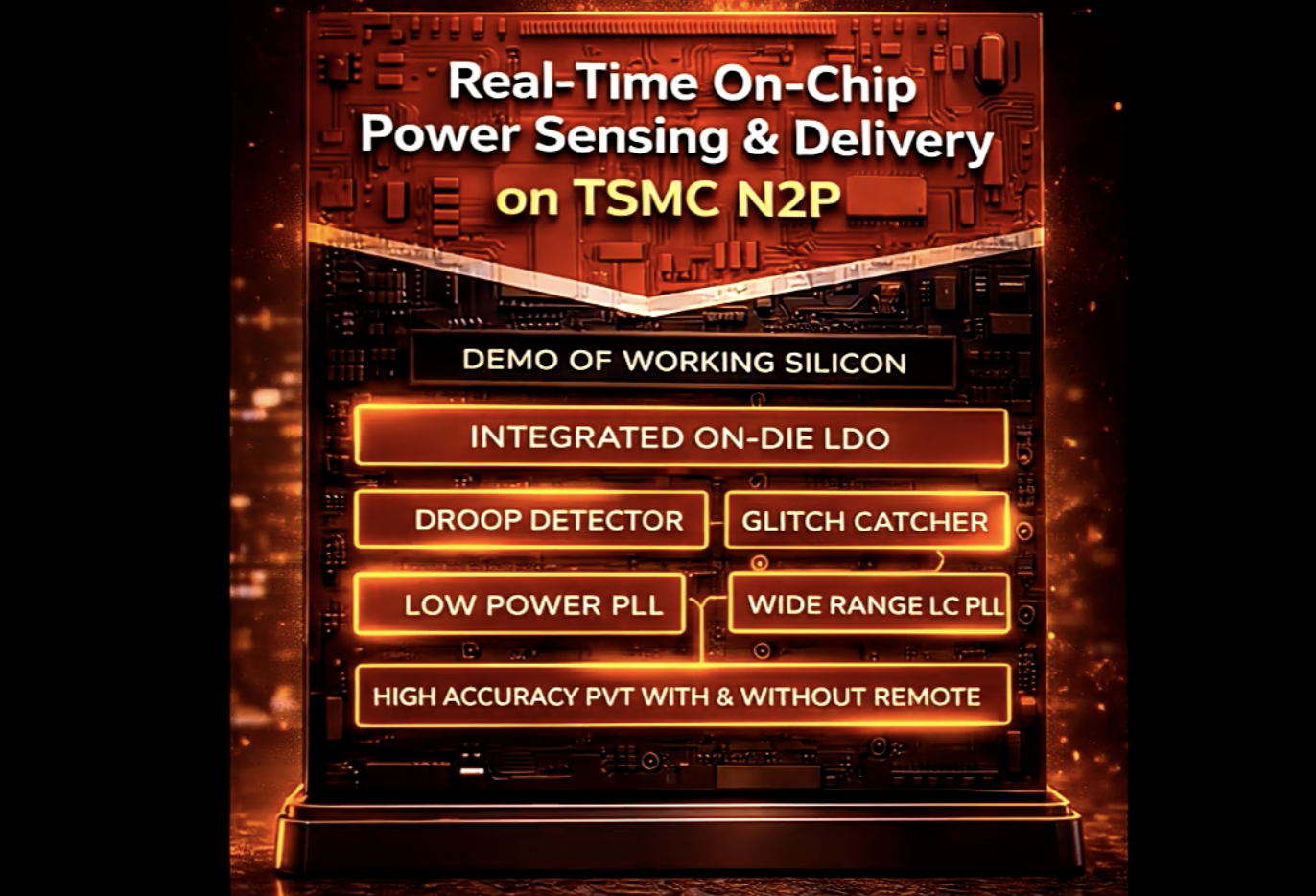

WEBINAR: Intrinsic Techniques in RF Power Amplifier DesignLoad-pull power amplifier (PA) design techniques determine the…Read More Analog Bits Demos Real-Time On-Chip Power Sensing and Delivery on N2P at the TSMC 2026 Technology SymposiumAnalog Bits has a way of stealing the…Read More

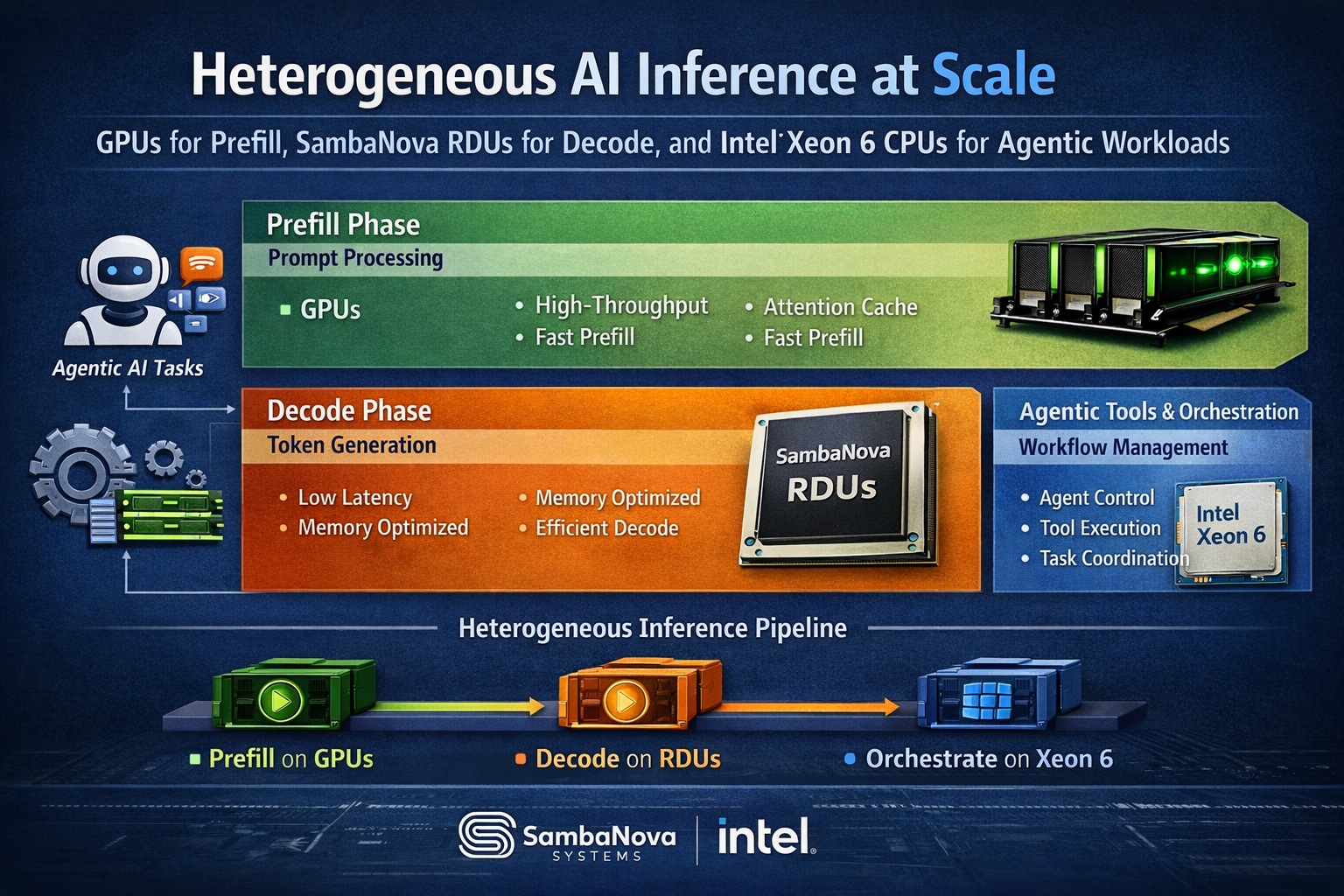

Analog Bits Demos Real-Time On-Chip Power Sensing and Delivery on N2P at the TSMC 2026 Technology SymposiumAnalog Bits has a way of stealing the…Read More Disaggregating LLM Inference: Inside the SambaNova Intel Heterogeneous Compute BlueprintSambaNova Systems and Intel have introduced a blueprint…Read More

Disaggregating LLM Inference: Inside the SambaNova Intel Heterogeneous Compute BlueprintSambaNova Systems and Intel have introduced a blueprint…Read More CEO Interview with Johan Wadenholt Vrethem of VoxoWith over two decades of experience bridging technology…Read More

CEO Interview with Johan Wadenholt Vrethem of VoxoWith over two decades of experience bridging technology…Read MoreSiFive to Power Next-Gen RISC-V AI Data Centers with NVIDIA NVLink Fusion

In a strategic move that could reshape the future of AI data center design, SiFive, a leading developer of RISC-V processor IP and compute subsystems, has announced plans to integrate NVIDIA’s NVLink Fusion interconnect technology into its high-performance data center platforms. This collaboration bridges the open-architecture… Read More

2026 Outlook with Dave Hwang of Alchip

Dr. Dave Hwang joined Alchip in 2021 as General Manager of Alchip’s North America Business Unit. He also serves as Senior Vice President, Business Development. Prior to join Alchip, Dave served as Vice President, Worldwide Sales and Marketing for Global Unichip and in a variety of management and technical roles at TSMC.

Tell

… Read MoreAgentic at the Edge in Automotive and Industry

It might seem from popular debate around AI and agentic that everything in this field is purely digital, initiated through text or voice prompts, often cloud-based or on-prem. But that view misses so much. AI is already an everyday experience at the edge, for voice-based control, in object detection and safety-triggered braking… Read More

TSMC’s CoWoS® Sustainability Drive: Turning Waste into Wealth

In a significant example of how high-tech manufacturing can embrace environmental stewardship without compromising operational excellence, Taiwan Semiconductor Manufacturing Company has launched a sustainability initiative within its advanced packaging operations that both reduces waste and generates meaningful… Read More

Podcast EP328:A Brief History of Chip Design and AI with Dr. Bernard Murphy

Daniel is joined by Dr. Bernard Murphy, a friend and fellow blogger on SemiWiki.

Dan explores some key milestones in Bernard’s journey in semiconductors and EDA, beginning with a focus on nuclear physics. Bernard explains how he developed an interest in AI technology and applications. In this broad and informative discussion,… Read More

Taming Advanced Node Clock Network Challenges: Duty Cycle

As process nodes advance, circuit behavior becomes progressively more challenging to analyze and predict. Few systems reflect this challenge more clearly than the clock network. These large, complex networks no longer behave as ideal digital signals. Instead, they operate as distributed electrical systems shaped by non-linear… Read More

2026 Outlook with Krishna Anne of Agile Analog

Tell us a little bit about yourself and your company.

I have worked in the global semiconductor industry for over 30 years, with major semiconductor companies such as Rambus, AMD and Broadcom, as well as with start-ups such as SCI Semiconductor and DataTrails. I started my career as a digital circuit designer, then moved into marketing,… Read More

CEO Interview with Dr. Heinz Kaiser of Schott

With over 25 years of experience in the specialty materials industry, Dr. Heinz Kaiser is a member of the Management Board of SCHOTT AG, responsible for High-Performance Materials and Flat Glass, while also heading Sales and Market Development, Sales Excellence, and Intellectual Property. With a strong engineering background… Read More

PQShield on Preparing for Q-Day

Following my series on quantum computing (QC), it is timely to look again at what is still the most prominent real-world concern around this technology: its ability to hack classical security methods for encryption and related tasks. Given what I have written on the topic, an understandable counter would be that QC is still in development… Read More

Is Intel About to Take Flight?