Semidynamics has taken a significant step forward in the race to build next-generation AI infrastructure with the unveiling of its 3nm AI inference silicon and a vertically integrated, full-stack systems strategy. Announced in February 2026, the development marks the company’s evolution from an advanced architecture specialist… Read More

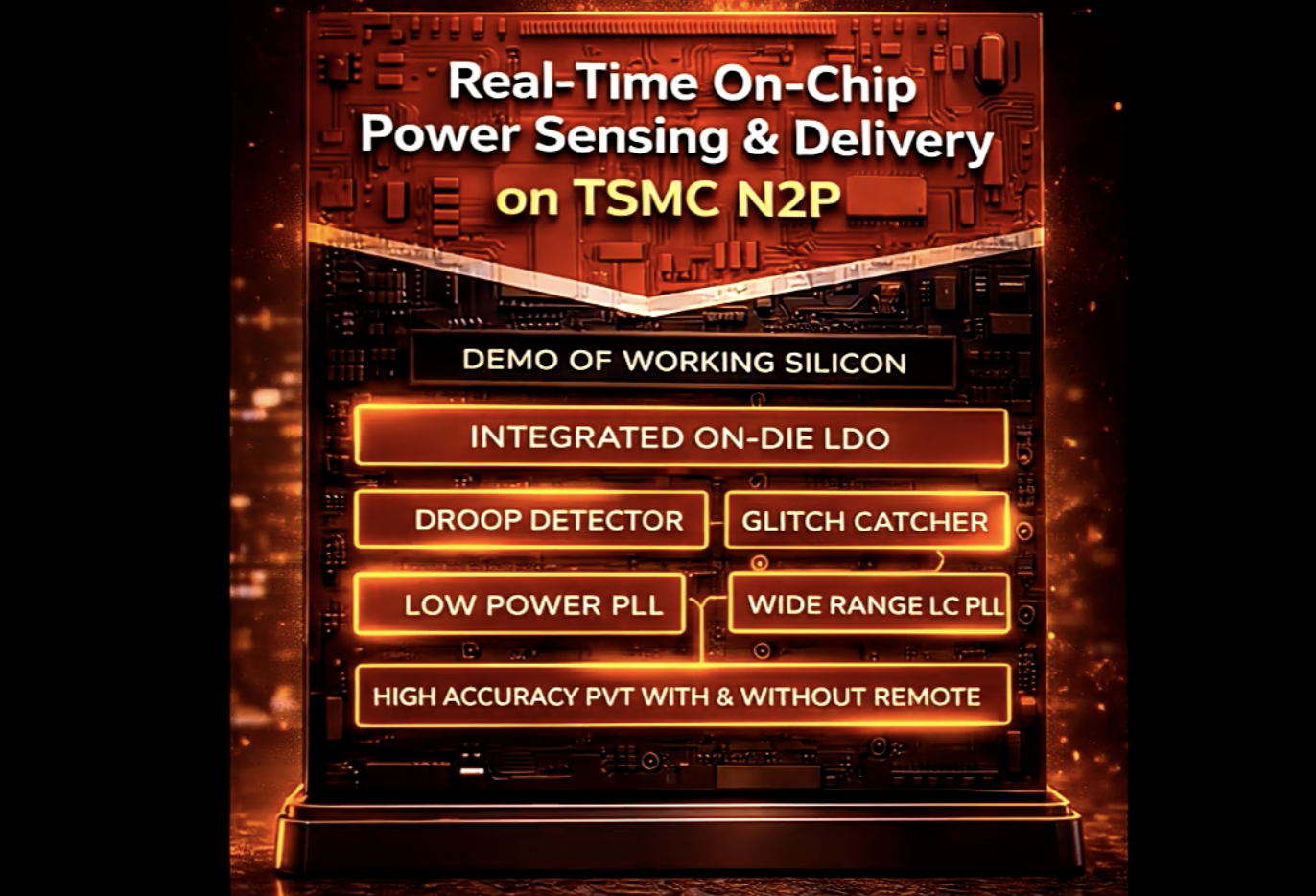

Analog Bits Demos Real-Time On-Chip Power Sensing and Delivery on N2P at the TSMC 2026 Technology SymposiumAnalog Bits has a way of stealing the…Read More

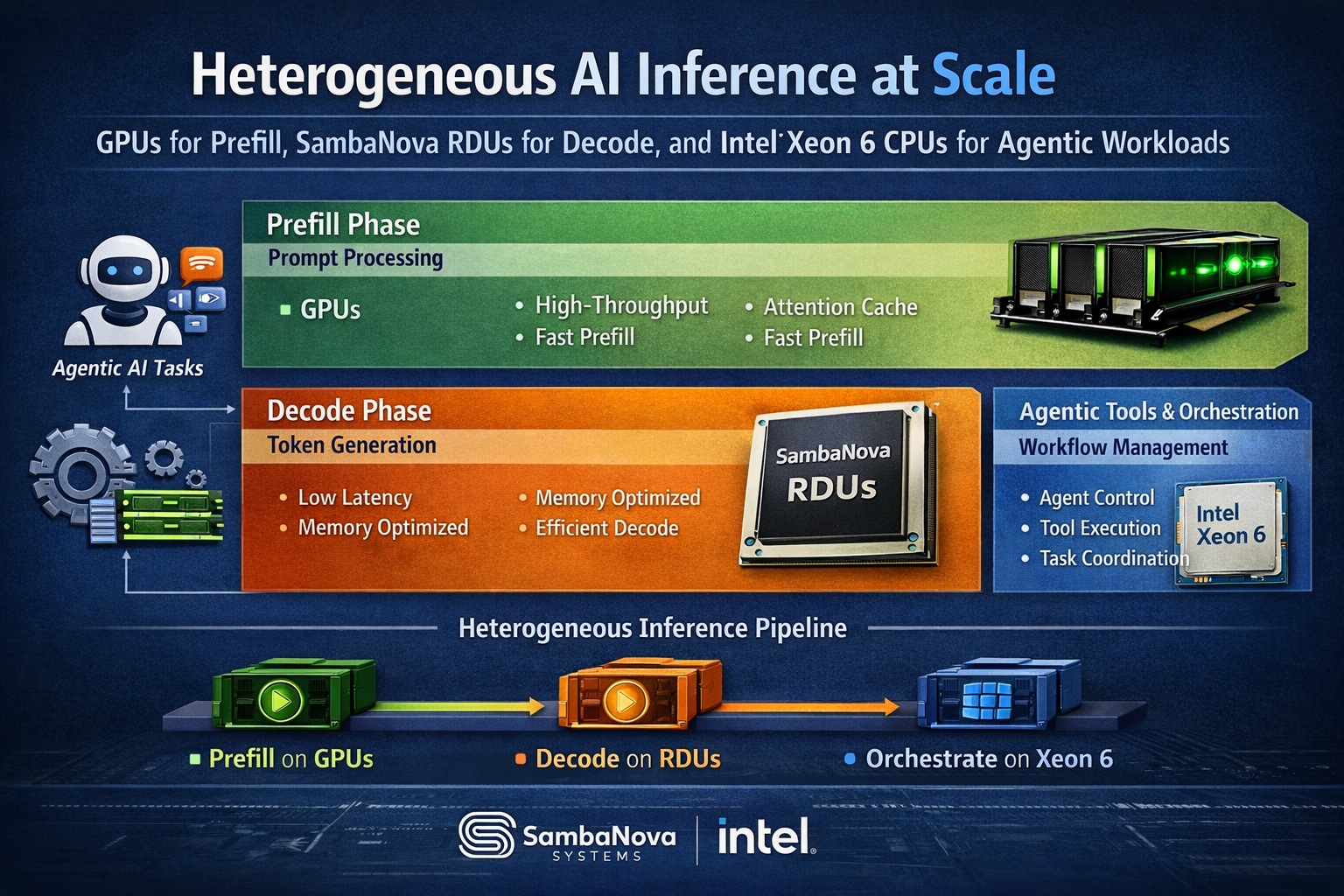

Analog Bits Demos Real-Time On-Chip Power Sensing and Delivery on N2P at the TSMC 2026 Technology SymposiumAnalog Bits has a way of stealing the…Read More Disaggregating LLM Inference: Inside the SambaNova Intel Heterogeneous Compute BlueprintSambaNova Systems and Intel have introduced a blueprint…Read More

Disaggregating LLM Inference: Inside the SambaNova Intel Heterogeneous Compute BlueprintSambaNova Systems and Intel have introduced a blueprint…Read More CEO Interview with Johan Wadenholt Vrethem of VoxoWith over two decades of experience bridging technology…Read More

CEO Interview with Johan Wadenholt Vrethem of VoxoWith over two decades of experience bridging technology…Read More TSMC to Elon Musk: There are no Shortcuts in Building Fabs!The opening of the TSMC 2026 earning call…Read More

TSMC to Elon Musk: There are no Shortcuts in Building Fabs!The opening of the TSMC 2026 earning call…Read More Speculation: Silicon’s Most Expensive CompulsionHow Time-Based Scheduling Reclaims Silicon Wasted by Speculative…Read More

Speculation: Silicon’s Most Expensive CompulsionHow Time-Based Scheduling Reclaims Silicon Wasted by Speculative…Read MoreWatch Live Agentic Software Debug

Many moons ago in the Innovation series we explored techniques like spectrum analysis to root-cause bugs. While these methods provide some value they don’t get as close as we would like to isolating a root-cause. In hindsight given what we know about the complexity of conventional debug it is unsurprising that we can’t root-cause… Read More

Accellera Strengthens Industry Collaboration and Standards Leadership at DVCon U.S. 2026

At DVCon U.S. 2026, Accellera Systems Initiative reinforces its central role in shaping the future of electronic design and verification through a focused program of workshops, tutorials, and community engagement. As system complexity continues to rise across AI, automotive, HPC, and communications markets, the need for… Read More

Ceva Wi-Fi 6 and Bluetooth IPs Power Renesas’ First Combo MCUs for IoT and Connected Home

The rapid expansion of IoT, smart home, and industrial automation markets is reshaping how connectivity is designed into embedded systems. Developers increasingly require highly integrated wireless solutions that deliver strong performance, ultra-low power consumption, and design flexibility, while also shortening… Read More

Why PDF Solutions Is Positioning Itself at the Center of the Semiconductor Ecosystem

The semiconductor industry is on track to exceed one trillion dollars in annual revenue by the end of the decade, propelled by AI, advanced computing, and edge applications. Yet beneath this growth lies a structural shift. Manufacturing complexity is rising faster than the industry’s ability to manage it. As architectures move… Read More

Chiplets Reach an Architectural Turning Point at Chiplet Summit 2026

The semiconductor industry’s transition toward chiplet-based architectures is entering a decisive new phase. What began as a promising alternative to SoC design is now confronting real-world demands around system integration, validation, and long-term scalability. At Chiplet Summit 2026, taking place February 17–19 … Read More

Gate-All-Around (GAA) Technology for Sustainable AI

The transition from FinFET to Gate-All-Around (GAA) transistor technology represents a pivotal moment in the evolution of logic devices, driven by both physical scaling limits and the rapidly growing computational demands of artificial intelligence. As semiconductor technology approaches the sub-3 nm regime, traditional… Read More

VSORA Board Chair Sandra Rivera on Solutions for AI Inference and LLM Processing

Sandra Rivera, a Silicon Valley veteran who is the former CEO of Altera, an Intel FPGA spinout, and long-time Intel executive, recently became Chair of the Board of Directors of Paris-based VSORA. VSORA, a technology leader redefining AI inference for next-generation data centers, cloud infrastructure and edge, is focused … Read More

TSMC & GCU Semiconductor Training Program: Preparing Tomorrow’s Workforce

The expansion of semiconductor manufacturing in the United States, particularly with TSMC’s multi-fab campus in Phoenix, Arizona, has created a significant need for skilled technical workers. To meet this demand, TSMC has partnered with educational institutions, including Grand Canyon University (GCU), to launch… Read More

CEO Interview with Dr. Raj Gautam Dutta of Silicon Assurance

Dr. Raj Gautam Dutta is the Co-Founder and Chief Executive Officer of Silicon Assurance, where he defines the company’s strategic direction and leads its technology and product vision. He is responsible for driving the development of differentiated hardware security solutions, executing growth and partnership strategies,… Read More

Is Intel About to Take Flight?