Recent independent teardown and technical analyses have confirmed that the 5G mmWave antenna module powering Apple’s latest iPhone 17 lineup relies on advanced SOITEC based Fully Depleted Silicon-On-Insulator (FD-SOI) substrate technology. The discovery highlights a significant architectural shift in high-frequency… Read More

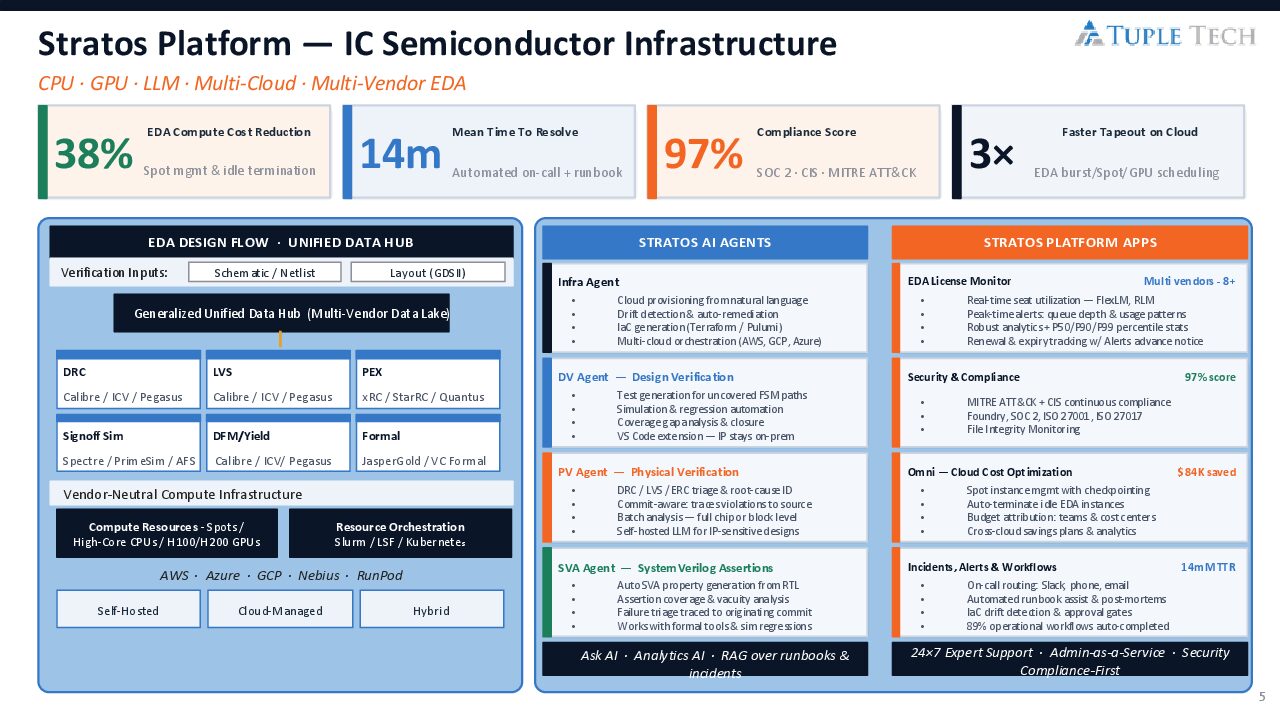

Rethinking ECAD IT Infrastructure: From Fragmentation to an Engineering PlatformThe semiconductor industry is entering a new phase…Read More

Rethinking ECAD IT Infrastructure: From Fragmentation to an Engineering PlatformThe semiconductor industry is entering a new phase…Read MoreAnother Quantum Topic: Quantum Communication

In my recent series on quantum computing (QC), I intentionally overlooked a couple of adjacent topics: quantum communication and quantum sensing. These face some of the same challenges as QC, however I noticed a recent report on a test quantum network implemented by Cisco and Qunnect which led me to find more from Cisco on their … Read More

Advancing Automotive Memory: Development of an 8nm 128Mb Embedded STT-MRAM with Sub-ppm Reliability

The rapid evolution of automotive technology has intensified the demand for highly reliable, high-performance semiconductor memory solutions. Modern vehicles increasingly rely ADAS driving features, and complex infotainment platforms, all of which require memory that can operate flawlessly under extreme environmental… Read More

Podcast EP333: A Look at the Broad, Worldwide Impact SEMI Has on the Semiconductor Industry with Ajit Manocha

Daniel is joined by Ajit Manocha, president and CEO of SEMI, the global industry association serving the semiconductor and electronics manufacturing and design supply chain. Throughout his career, Manocha has been a champion of industry collaboration as a critical means of advancing technology for societal and economic prosperity.… Read More

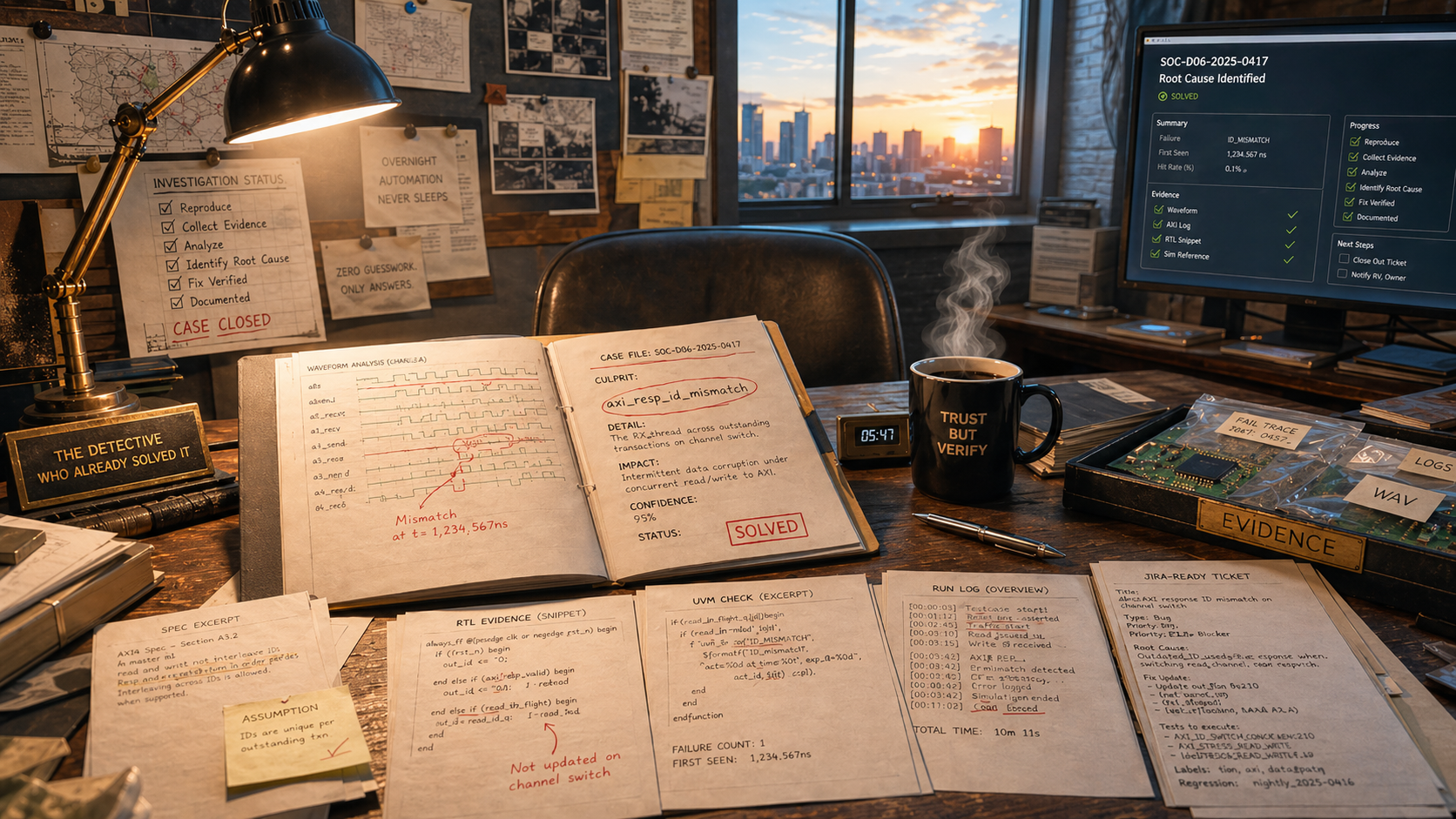

Memory Matters: Signals from the 2025 NVM Survey

Non-volatile memory choices are becoming more complex as SoC designs push into advanced nodes, and new requirements driven by AI, new sensor technologies and stringent quality standards.

The second annual 2025 NVM Survey, completed in December, captures a market that still hangs on established technologies but is increasingly… Read More

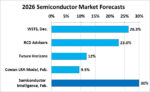

AI Drives Strong Semiconductor Market in 2025-2026

The global semiconductor market in 2025 was $792 billion, according to WSTS. 2025 was up 25.6% from 2024, the strongest growth since 26.2% in the COVID recovery year 2021. The increase was driven by AI, with Nvidia revenues up 65%. The major memory companies (Samsung, SK Hynix, Micron Technology, Kioxia and Sandisk) all cited AI… Read More

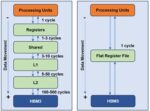

How Customized Foundation IP Is Redefining Power Efficiency and Semiconductor ROI

As computing expands from data centers to edge devices, semiconductor designers face increasing pressure to optimize both performance and energy efficiency. Advanced process nodes continue to provide transistor-level improvements, but scaling alone cannot meet the demands of hyperscale AI infrastructure or ultra-low-power… Read More

Akeana Partners with Axiomise for Formal Verification of Its Super-Scalar RISC-V Cores

An AI-Native Architecture That Eliminates GPU Inefficiencies

A recent analysis highlighted by MIT Technology Review puts the energy cost of generative AI into stark perspective. Generating a simple text response from Llama 3.1-405B—a model with 405 billion parameters, the adjustable “knobs” that enable prediction—requires on average 3,353 joules, nearly 1 watt-hour (Wh). Once cooling… Read More

Caspia Technologies Unveils A Breakthrough in RTL Security Verification Paving the Way for Agentic Silicon Security

In a significant advancement for the semiconductor industry, Caspia Technologies announced the broad availability of CODAx V2026.1, its flagship RTL security analyzer. The new release strengthens early-stage hardware security verification and positions the company to deliver fully agentic workflows that automate vulnerability… Read More

Siemens U2U 3D IC Design and Verification Panel