At the recent TSMC Technology Symposium 2026, Siemens EDA reinforced its position as one of the key ecosystem partners supporting TSMC in the race toward AI-driven semiconductor design, advanced packaging, and next-generation process technologies. The annual forum has become one of the semiconductor industry’s most important… Read More

SiFive’s P570 Gen 3 Pushes RISC-V Further Into the AI EraWith the launch of its new P570 Gen…Read More

SiFive’s P570 Gen 3 Pushes RISC-V Further Into the AI EraWith the launch of its new P570 Gen…Read More CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read More

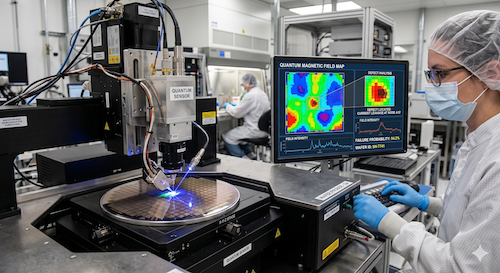

CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read More Sensing. A Quantum Tech Ready for Market?While the quantum world revolves around quantum computing,…Read More

Sensing. A Quantum Tech Ready for Market?While the quantum world revolves around quantum computing,…Read More #DAC2026 Marks Another Pivotal Moment for the Semiconductor IndustryThe 2026 Design Automation Conference (DAC 2026) marks…Read More

#DAC2026 Marks Another Pivotal Moment for the Semiconductor IndustryThe 2026 Design Automation Conference (DAC 2026) marks…Read MoreSemidynamics Secures a Strategic Investment to Advance Memory-Centric AI Inference Chips

In the rapidly evolving world of artificial intelligence hardware, memory bandwidth and data movement have become just as important as raw compute power. Addressing this challenge head-on, Semidynamics has announced a strategic investment aimed at accelerating the development of its next-generation memory-centric AI … Read More

Quantum Gathering Momentum Amid Concerns for the Grid

I posted recently on an eye-catching advance in quantum computing, around neutral atom systems which might accelerate the transition to production-grade fault-tolerant quantum computing (QC). There are some further updates on this front, also I listened in on a panel considering quantum-based hacking vulnerability in the… Read More

PQShield unveils ultra-small PQC embedded security breakthroughs at Embedded World 2026

As the threat of quantum computing to modern cybersecurity becomes increasingly real, the technology industry is accelerating efforts to develop cryptographic systems capable of resisting quantum attacks. One of the most significant developments in this field was presented at Embedded World 2026 in Nuremberg, Germany, … Read More

Closing the Silicon Realization Gap: From Static DFM to Governance for Lifecycle (GFL)

The semiconductor industry has achieved extraordinary mastery in silicon signoff. Modern EDA environments can now optimize timing closure, physical verification, IR/EM behavior, routing density, thermal interaction, and increasingly even design-space exploration through AI-assisted implementation flows. Crossing… Read More

imec IC-Link and TSMC 3DFabric Alliance Expansion Signals New Era of System-Level Scaling

imec announced that IC-Link by imec has joined the TSMC 3DFabric Alliance, a strategically important move that reflects the semiconductor industry’s transition from traditional monolithic scaling toward heterogeneous integration, chiplet architectures, and advanced packaging-driven system optimization. The partnership… Read More

Crossing the Yield Cliff: IDP V6 and the Future of Manufacturing Forecasting

The paper, Industrial Defectivity Prediction (IDP) V6: A Two-Layer Yield Cliff Framework for Cross-Industry Mass-Production Forecasting, presents a generalized industrial yield-modeling architecture that extends the classical Negative Binomial framework through a two-layer phenomenological structure designed … Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior

At CES 2026, Samsung called it a “companion.” Lenovo called it “ambient intelligence.” OpenAI spent $6.4 billion on a screenless device designed to be a continuous presence in your pocket. Meta acquired Limitless, the AI pendant that had been tracking everything its wearers said and heard. Every major consumer electronics company… Read More

AI Chip Design Moves Beyond Monolithic Silicon with Alchip 3DIC

Artificial intelligence processors are entering a new era. For more than two decades, semiconductor innovation was driven primarily by transistor scaling and process node shrinks. Today, however, AI infrastructure demands are growing faster than traditional Moore’s Law improvements can sustain. The industry is now shifting… Read More

CEO Interview with RP Singh of Seasia Infotech

Rupinder Pal Singh is the co-founder and CEO of Seasia Infotech, a role he takes great pride in. Sharing insights into the business and industry is something he always looks forward to. As the leader of the Seasia Group of Companies, Singh is tasked with overseeing all aspects of operations, ensuring that the company delivers… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior