Subsystem and full-chip integration plays a crucial role in any project – particularly for large SoCs. Our upcoming webinar on April 30 confronts the typical challenges of this process and provides a detailed view into how IP centric design can help you solve them. Join us to learn how transforming your design flow can help your… Read More

Sensors Converge: Where Intelligence Meets the EdgeThe Sensors Converge Conference is one of the…Read More

Sensors Converge: Where Intelligence Meets the EdgeThe Sensors Converge Conference is one of the…Read More Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data CenterAt the TERAFAB launch event in Austin on…Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data CenterAt the TERAFAB launch event in Austin on…Read More Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read MoreThe Data Crisis is Unfolding – Are We Ready?

The rapid advancement of technology, including generative AI, IoT, and autonomous vehicles, is revolutionizing industries and enhancing efficiency. At the same time, such advances also generate huge amounts of data to be transmitted and processed to make sense and provide value to consumers and society as a whole. In essence,… Read More

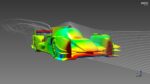

Simulation World 2024 Virtual Event

ANSYS Simulation World is an annual conference hosted by ANSYS, Inc., a leading provider of engineering simulation software. The event typically brings together engineers, designers, researchers, and industry experts from around the world to discuss the latest advancements, best practices, and case studies in engineering… Read More

Podcast EP216: Q4 2023 is Another Strong Growth Quarter for EDA as Reviewed by Wally Rhines

Dan is joined by Dr. Walden Rhines. Wally is a lot of things, CEO of Cornami, board member, advisor to many and friend to all. In this session, he is the Executive Sponsor of the SEMI Electronic Design Market Data Report.

Wally reviews the Electronic Design Market Data report that was just released for Q4 2023. Growth continues to be… Read More

Synopsys Presents AI-Fueled Innovation at SNUG 2024

SNUG is the premier event for Synopsys to showcase its technology and impact on the industry. This year’s SNUG did not disappoint. The two-day event packed many fantastic user presentations along with exciting news of innovation from Synopsys. Jensen Huang and Sassine Ghazi even held a live, interactive Q&A session. Compelling… Read More

Podcast EP215: A Tour of the GlobalFoundries Silicon Photonics Platform with Vikas Gupta

Dan is joined by Vikas Gupta, senior director of product management at GlobalFoundries focused on Silicon Photonics and ancillary technologies. Vikas has close to 30 years of semiconductor experience with TI, Xilinx, AMD, GlobalFoundries, POET Technologies, and back to GlobalFoundries.

Vikas discusses the growing demands… Read More

CEO Interview with Ninad Huilgol of Innergy Systems

Ninad Huilgol is the Founder and CEO at Innergy Systems, has extensive experience in design verification of ultra low-power mobile SoCs. Previously, he has worked in senior engineering management at various semiconductor companies such as Broadcom and Synopsys. He has multiple power- and design-related patents, trade secrets… Read More

sureCore Brings 16nm FinFET to Mainstream Use With a New Memory Compiler

Semiconductor processes can have a rather long and interesting life cycle. At first, a new process defines the leading edge. This is cost-no-object territory, where performance is king. The process is new, the equipment to make it is expensive, and its use is reserved for those that have a market (and budget) big enough to justify… Read More

Are Agentic Workflows the Next Big Thing in AI?

AI continues to be a fast-moving space and we’re always looking for the next big thing. There’s a lot of buzz now around something called agentic workflows – ugly name but a good idea. LLMs had a good run as the state-of-the-AI-art, however evidence is building that the foundation model behind LLMs alone has limitations, both theoretically… Read More

Navigating the Complexities of Software Asset Management in Modern Enterprises

In today’s digital age, software has become the backbone of modern enterprises, powering critical operations, driving innovation, and facilitating collaboration. However, with the proliferation of software applications and the complexity of licensing models, organizations are facing significant challenges … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center