When it comes to the security of tomorrow, the time to prepare is today, and at PQShield, we’re focused on shaping the way the digital world is protected from the inevitable quantum threat. We deliver real-world, quantum-safe hardware and software upgrades, and it’s our mission to help modernize the legacy security systems and

Sensors Converge: Where Intelligence Meets the EdgeThe Sensors Converge Conference is one of the…Read More

Sensors Converge: Where Intelligence Meets the EdgeThe Sensors Converge Conference is one of the…Read More Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data CenterAt the TERAFAB launch event in Austin on…Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data CenterAt the TERAFAB launch event in Austin on…Read More Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read MoreWEBINAR: Navigating the Power Challenges of Datacenter Infrastructure

We all know power and energy management is a top-of-mind item for many, if not all new system designs. Optimizing system power is a vexing problem. Success requires coordination of many hardware and software activities. The strategies to harmonize operation for high performance and low power are often not obvious. Much… Read More

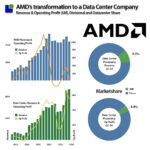

Nvidia Sells while Intel Tells

AMD’s Q1-2024 financial results are out, prompting us to delve into the Data Center Processing market. This analysis, usually reserved for us Semiconductor aficionados, has taken on a new dimension. The rise of AI products, now the gold standard for semiconductor companies, has sparked a revolution in the industry, making… Read More

Anirudh Keynote at CadenceLIVE 2024. Big Advances, Big Goals

The great things about CEO keynotes, at least from larger companies, is that you not only learn about recent advances but you also get a sense of the underlying algorithm for growth. Particularly reinforced when followed by discussions with high profile partner CEOs on their directions and areas of common interest. I saw this recently… Read More

Will my High-Speed Serial Link Work?

PCB designers can perform pre-route simulations, follow layout and routing rules, hope for the best from their prototype fab, and yet design errors cause respins which delays the project schedule. Just because post-route analysis is time consuming doesn’t mean that it should be avoided. Serial links are found in many PCB designs,… Read More

Enabling Imagination: Siemens’ Integrated Approach to System Design

In today’s rapidly advancing technological landscape, semiconductors are at the heart of innovation across diverse industries such as automotive, healthcare, telecommunications, and consumer electronics. As a leader in technology and engineering, Siemens plays a pivotal role in empowering the next generation … Read More

Ceva Accelerates IoT and Smart Edge AI with a New Wireless Platform IP Family

Ceva is a very focused company. In its words, the leader in innovative silicon and software IP solutions that enable smart edge products to connect, sense, and infer data more reliably and efficiently. You can see some of its accomplishments here. The company has been licensing IP for more than twenty years with more than 17 billion… Read More

LRCX- Mediocre, flattish, long, U shaped bottom- No recovery in sight yet-2025?

– Lam reports another flat quarter & guide- No recovery in sight yet

– Seems like no expectation of recovery until 2025- Mixed results

– DRAM good- NAND weak- Foundry/Logic mixed-Mature weakening

– Clearly disappointing to investors & stock hoping for a chip recovery

Another Flat Quarter &

… Read MoreWEBINAR: The Rise of the DPU

The server and enterprise network boundary has seen complexity explode in recent years. What used to be a simple TCP/IP offload task for network interface cards (NICs) is transforming into full-blown network acceleration using a data processing unit (DPU), able to make decisions based on traffic routes, message content, and… Read More

Podcast EP220: The Impact IQE’s Compound Semiconductors Are Having on the Industry with Dr. Rodney Pelzel

Dan is joined by Dr. Rodney Pelzel, he has over 20 years of experience in the semiconductor industry, with deep expertise in semiconductor materials engineering and the epitaxial growth of compound semiconductors. Dr. Pelzel joined IQE as a Production Engineer in 2000 and is now head of R&D and is tasked with creating unique… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center