TechInsights has been in the semiconductor analysis business for more than 35 years and is THE most trusted source of semiconductor information. TechInsights started as a reverse engineering and IP analysis company but has grown into much more. I remember waiting for the teardown reports before buying electronics to make sure… Read More

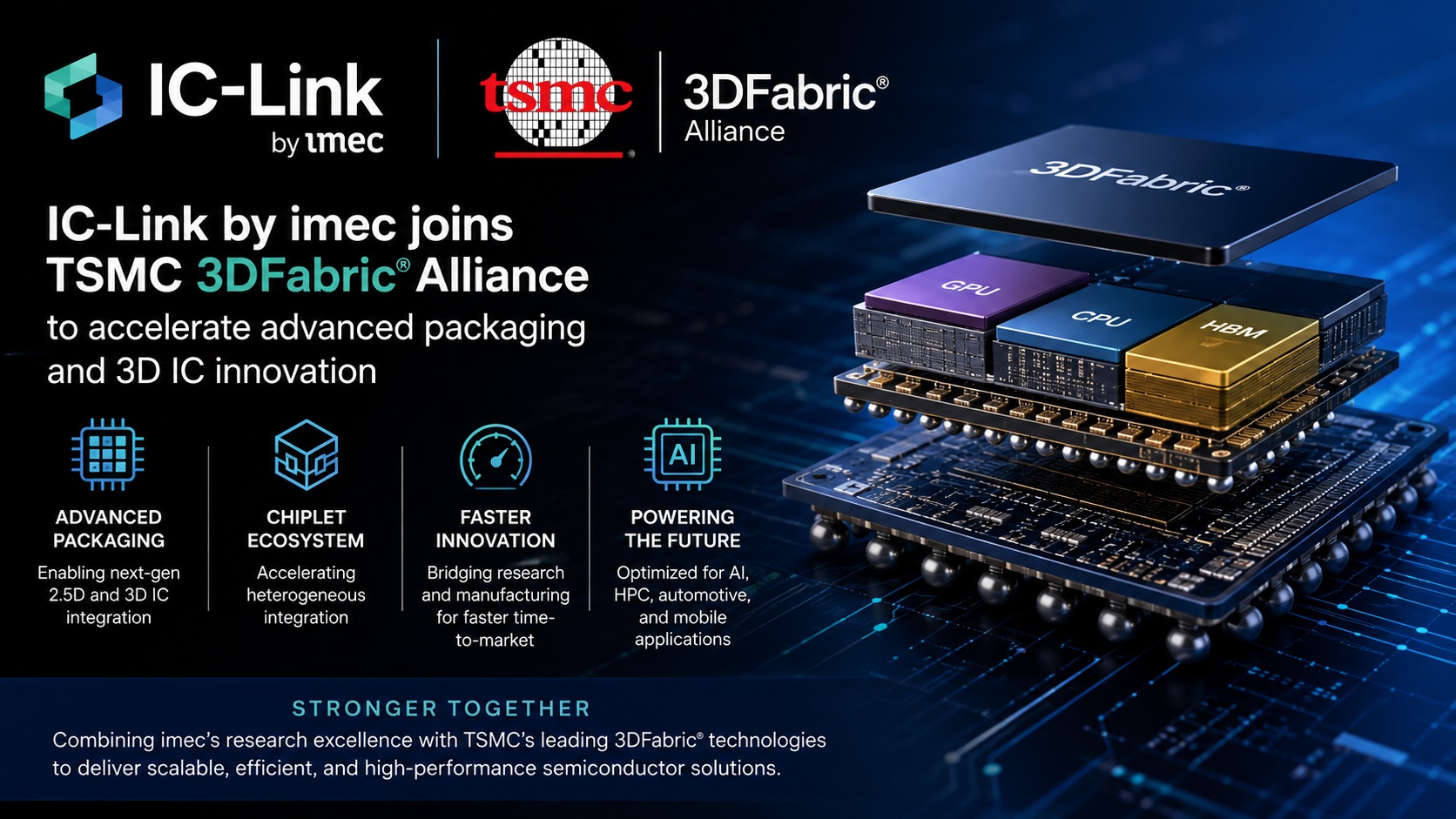

imec IC-Link and TSMC 3DFabric Alliance Expansion Signals New Era of System-Level Scalingimec announced that IC-Link by imec has joined…Read More

imec IC-Link and TSMC 3DFabric Alliance Expansion Signals New Era of System-Level Scalingimec announced that IC-Link by imec has joined…Read More From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More

From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More

TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More

CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read MoreAccelerating Automotive SoC Design with Chiplets

The automotive industry is evolving rapidly with the increasing demand for intelligent, connected, and autonomous vehicles. Central to this transformation are System-on-Chip (SoC) designs, which integrate multiple processing units into a single chip for managing everything from safety systems to in-car entertainment.… Read More

AI PC momentum building with business adoption anticipated

And just like that, the AI PC arrived. It will be hard to miss high-profile advertising campaigns like the one just launched by Microsoft touting them. Gartner said this September that AI PCs will be 43% of all PC shipments in 2025 (with 114M units projected) and that by 2026, AI PCs will be the only choice for business laptop users. … Read More

Happy New Year from SemiWiki

As SemiWiki celebrates our 14th anniversary I wanted to wish you all a happy New Year! Working in the semiconductor industry for the past 40 years has been rewarding beyond belief. Working in the trenches and traveling the world has been an education in itself, more so than any other career that I could imagine. SemiWiki has broadened… Read More

CEO Interview: Subi Krishnamurthy of PIMIC

Subi Krishnamurthy is the Founder and CEO of PIMIC, an AI semiconductor company pioneering processing-in-memory (PiM) technology for ultra-low-power AI solutions. With over 30 years of experience in silicon design and product development, Subi has led the mass production of 12+ silicon projects and holds 30+ patents. He began… Read More

CEO Interview: Dr Josep Montanyà of Nanusens

Dr. Josep Montanyà Chief Executive Officer – UK/Spain Co-founder leading the company, with +18 years of experience in MEMS, patents and the semiconductor industry. Founded Baolab Microsystems prior to Nanusens.

Tell us a little bit about your company?

We have a patented technology that allows us to build chips with nano-mechanisms… Read More

Accelerating Simulation. Innovation in Verification

Following a similar topic we covered early last year, here we look at updated research to accelerating RTL simulation through domain-specific hardware. Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO and lecturer at Stanford, EE292A) and I continue our … Read More

Podcast EP268: A Decade in the Chinese Semiconductor Industry: An American’s Story

Dan is joined Dr. Douglas Sparks, CEO of M2N Technologies LLC, a consulting firm specializing in semiconductors, MEMS and sensors, including their supply chains. He has just published a new book, A Decade in the Chinese Semiconductor Industry: An American’s Story. Doug was the CTO of Hanking Electronics which built a high-volume… Read More

The Intel Common Platform Foundry Alliance

When I do a root cause analysis of Intel’s problem it is very simple. If Intel wants to continue to be a leading-edge semiconductor manufacturer, they need to fill their fabs, all of their fabs. Clearly several things need to happen in order to do that but the one that most interests me is on the foundry side.

I think we can all agree that… Read More

CEO Interview: Marc Engel of Agileo Automation

Marc Engel has served as the CEO of Agileo Automation for the past 15 years. Agileo specializes in software solutions for controlling semiconductor production equipment and connecting tools to MES systems using SECS/GEM and OPC-UA standards. Marc started his extensive 25-year engineering career in software development on… Read More

Crossing the Yield Cliff: IDP V6 and the Future of Manufacturing Forecasting