Consensia, a Dassault Systemès channel partner, recently hosted a webinar on DesignSync, a long-standing pillar of many industry design flows (count ARM, Qualcomm, Cavium and NXP among their users). A motivation for this webinar was the impact semiconductor consolidation has had on the complexity of design data management,… Read More

Basilisk at Hot Chips 2025 Presented Ominous Challenge to IP/EDA Status QuoAt Hot Chips 2025, Philippe Sauter of ETH…Read More

Basilisk at Hot Chips 2025 Presented Ominous Challenge to IP/EDA Status QuoAt Hot Chips 2025, Philippe Sauter of ETH…Read More GlobalFoundries 2025 Update GTS25"GTS25 brings together leaders from across the semiconductor…Read More

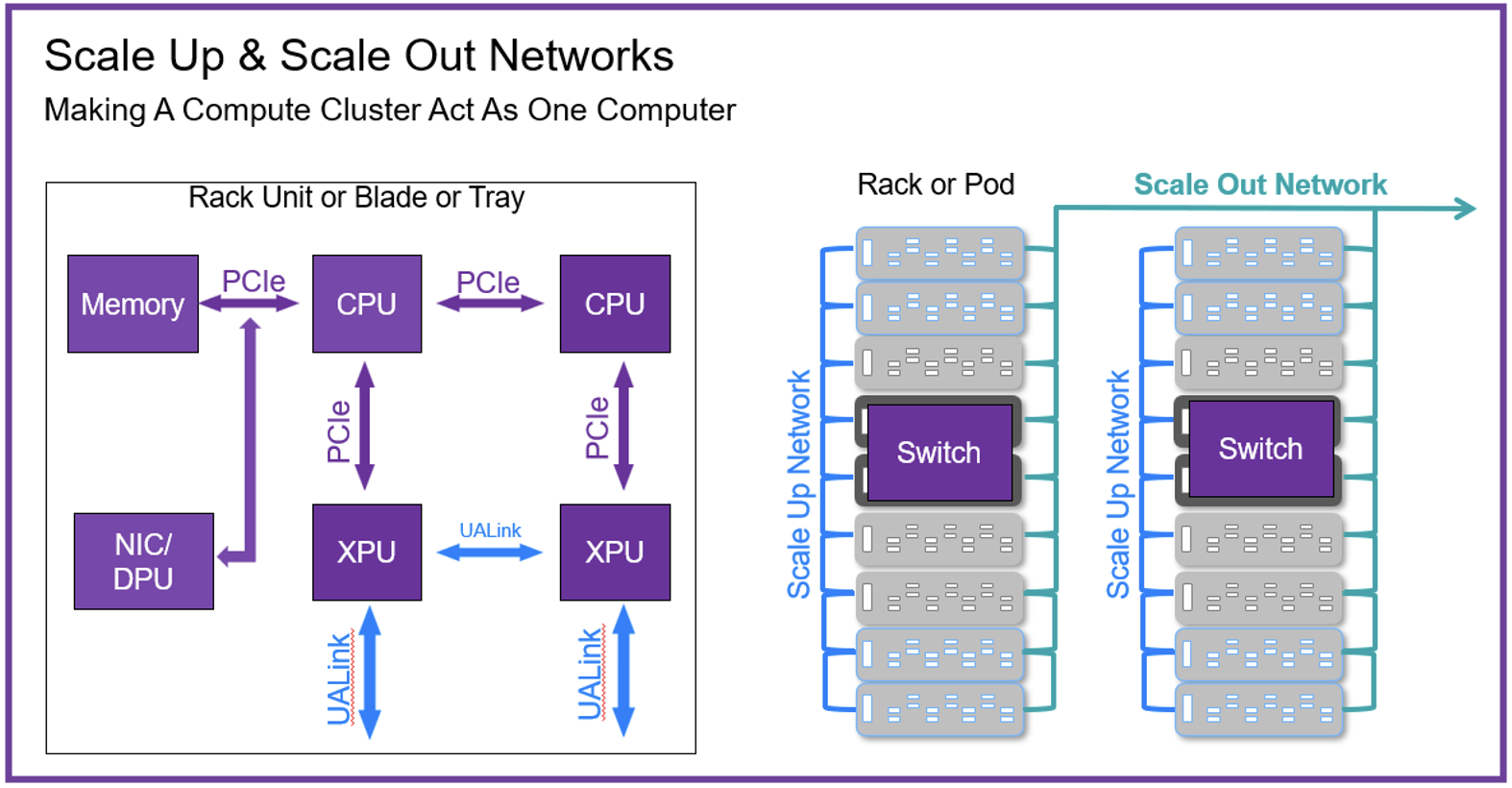

GlobalFoundries 2025 Update GTS25"GTS25 brings together leaders from across the semiconductor…Read More Synopsys Enables AI Advances with UALinkThe evolution of hyperscale data center infrastructure to…Read More

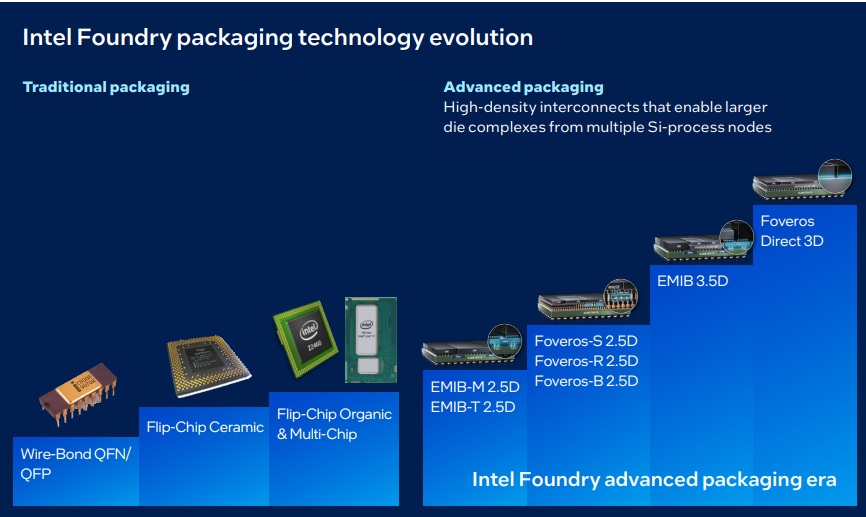

Synopsys Enables AI Advances with UALinkThe evolution of hyperscale data center infrastructure to…Read More Revolutionizing Chip Packaging: The Impact of Intel's Embedded Multi-Die Interconnect Bridge (EMIB)In an era dominated by artificial intelligence (AI),…Read More

Revolutionizing Chip Packaging: The Impact of Intel's Embedded Multi-Die Interconnect Bridge (EMIB)In an era dominated by artificial intelligence (AI),…Read MoreUnderstanding Sources of Clock Jitter Critical for SOC’s

Jitter issues in SOC’s reside at the crossroads of analog and digital design. Digital designers would prefer to live in a world of clocks that are free from jitter effects. At the same time, analog designers can build PLL’s that are precise and finely tuned. However, when a perfectly working PLL is inserted into an SOC, things can … Read More

CEO Interview: Stanley Hyduke, founder and CEO of Aldec

Dr. Stanley Hyduke, founder and CEO of Aldec talks about how keeping pace with the evolution of FPGAs and listening to customers underpin the company’s success.… Read More

FD-SOI in Japan?

If you want to get your finger on the Japan FD-SOI pulse, registration is still open for a free, two-day workshop in Tokyo this week organized by the SOI Consortium. This is the 3rd Annual SOI Tokyo Workshop, and there’s a really interesting line-up of speakers.

In case you’re wondering, Japan is doing FD-SOI. In fact… Read More

Webinar -New Concepts in Semiconductor IP Lifecycle Management

The semiconductor IP market continues growing at a healthy rate, and IP reuse is a staple of all modern SoC designs. Along with the acceptance of IP reuse comes a host of growing challenges, like:

- Increase in design files

- Increase in meta-data

- More links between design members worldwide

- More links between data in multiple engineering

Three Major Challenges Facing IoT

The Internet of Things (IoT) — a universe of connected things providing key physical data and further processing of that data in the cloud to deliver business insights— presents a huge opportunity for many players in all businesses and industries . Many companies are organizing themselves to focus on IoT and the connectivity of… Read More

CPU, GPU, H/W Accelerator or DSP to Best Address CNN Algorithms?

If you read an article dealing with Convolutional Neural Network (CNN), you will probably hear about the battle between CPU and GPU, both off-the-shelf standard product. Addressing CNN processing needs with standard CPU or GPU is like having to sink a screw when you only have a hammer or a monkey wrench available. You can dissert… Read More

Time is Money, Especially when Testing ICs

Semiconductor companies are looking for ways to keep their business profitable by managing expenses on both the design and test side of electronic products, which is quite the challenge as the trends show increases in test pattern count and therefore test costs. Scan compression is a well-known technique first created over 15… Read More

Webinar: Getting to Accurate Power Estimates Earlier and Faster

Power has become a very important metric in modern designs – for mobile and IoT devices which must live on a battery charge for days or years, for datacenters where power costs can be as significant as capital costs, and for increasingly unavoidable regulatory reasons. But accurate power estimation on a design must start from an … Read More

CDC Verification for FPGA – Beyond the Basics

FPGAs have become a lot more capable and a lot more powerful, more closely resembling SoCs than the glue-logic we once considered them to be. Look at any big FPGA – a Xilinx Zynq, an Intel/Altera Arria or a Microsemi SmartFusion; these devices are full-blown SoCs, functionally different from an ASIC SoC only in that some of the device… Read More

Intel’s Pearl Harbor Moment