If you are designing an SOC for an IoT application and looking to minimize power consumption, there are a lot of choices. However, more often than not, looking at reducing SRAM power is a good place to start. SRAMs can consume up to 70% of an IC’s power. SureCore, a leading memory IP supplier, offers highly optimized SRAM instances for such applications. They took the approach of looking at first principles to effectively rethink how to reduce SRAM power. Making good use of their approach, they have developed memory compilers that deliver front and back end views of the memory instances required by their users. As part of this, accurate timing and power views are needed to complete designs incorporating these instances.

Designers utilizing SRAM instances look to Liberty model files to provide characterized timing and power information so that system level simulations are fully accurate. Generating this characterization data is computationally intensive according to sureCore. However, they make use of advanced tools and techniques to make the task manageable. In my conversations with them they discussed how they manage the characterization process for their EverOn 40ULP family of SRAM instances.

For each synchronous input, for a range of clock and data edge speeds (typically around 7 of each) they needed to examine 49 (7×7) setup and hold values. On the power side, they needed to look at static and dynamic power for operation modes such as read and write, as well as the full range of available power down and sleep modes. As you can see, this becomes an exponentially growing problem since different PVTs are added and consideration is given for each of the different configurations.

For each synchronous input, for a range of clock and data edge speeds (typically around 7 of each) they needed to examine 49 (7×7) setup and hold values. On the power side, they needed to look at static and dynamic power for operation modes such as read and write, as well as the full range of available power down and sleep modes. As you can see, this becomes an exponentially growing problem since different PVTs are added and consideration is given for each of the different configurations.

The EverOn[SUP]TM[/SUP] family consists of 276 different SRAM instances that vary in aspect ratio, word count and word length. The family’s operating range is between 0.6V and 1.21V, creating a large PVT space for full characterization. A brute force approach to simulation could easily require an unworkable 24 hours per instance. One aspect of their characterization solution is to take advantage of the most recent and advanced features of Liberate-MX provided by Cadence.

(Note: Is this too much of an ad for Cadence?)

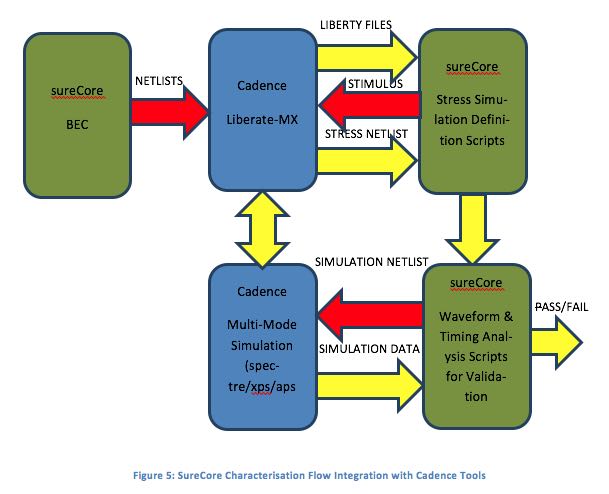

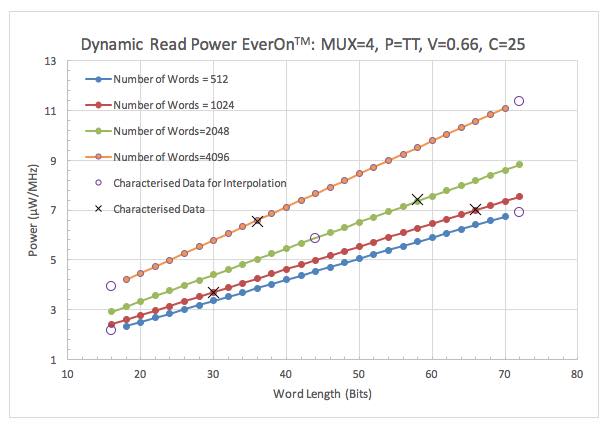

They explain how several features in Liberate-MX accelerate the process. First Liberate-MX can carefully prune the netlist during timing estimation to include only the circuit elements necessary to provide an accurate value of the timing parameter being characterized. The other technique they employ is using interpolation to provide power numbers over a wide range of memory configurations. SureCore has used full characterization runs on sample memory sizes to validate the interpolation results and has seen excellent correlation.

The Cadence tool suite is used to optimize runtime while maintaining accuracy. Liberate-MX cleverly dispatches leaf level pieces of the memory instance to Spectre XPS for detailed SPICE simulation results. With smaller process nodes there has been an increase in PVT corners, and Monte Carlo analysis is becoming necessary. The number of simulation runs needed has exploded. They use the new Cadence Super Sweep technology, leveraging simulation steps that can be shared between different corners that accelerates simulation. SureCore has seen a 2x speed up in runtime and an improvement in accuracy using these techniques.

The Cadence tool suite is used to optimize runtime while maintaining accuracy. Liberate-MX cleverly dispatches leaf level pieces of the memory instance to Spectre XPS for detailed SPICE simulation results. With smaller process nodes there has been an increase in PVT corners, and Monte Carlo analysis is becoming necessary. The number of simulation runs needed has exploded. They use the new Cadence Super Sweep technology, leveraging simulation steps that can be shared between different corners that accelerates simulation. SureCore has seen a 2x speed up in runtime and an improvement in accuracy using these techniques.

However, a substantial part of reducing their computational requirements for memory characterization come from the flow that sureCore has developed, including specific parasitic reduction techniques to deliver optimized netlists that provide optimal inputs to each step in the flow. They report dramatic reductions in netlist sizes for timing, static and dynamic power.

SureCore also focuses on validation to ensure the characterization flow is producing safe and accurate results. They have a scripted environment to check simulation results to ensure that the models perform properly. They even run checks that validate that the correct internal structures were included in the characterization runs. On top of this they run stressed simulations with Monte Carlo variation.

SureCore is filling a need for low power SRAM IP, which is critical for a variety of edge devices in a plethora of applications. I found it fascinating to learn about their comprehensive process dedicated to characterization. They have white papers on their website that offer interesting information on their technology. Without a flow like this, it would be a computational challenge to deliver high quality and consistent IP deliverables in a reasonable timeframe.

You may want to check-out more about this unique characterization methodology by clicking here or going to www.sure-core.com.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.