In sports, we’re all familiar with how even a team with the best individual players for every role needs to be coordinated as a team to win a championship. In healthcare, a patient is better served with a well-trained primary physician to coordinate with the various medical specialists. The field of semiconductors involves a series… Read More

Tag: characterization

Low Power Design – Art vs. Science

I have heard many times before that low power and mixed-signal design is more Art than Science. I believe this is a misconception. Science is a field that builds upon previous experiences and discoveries. Art primarily seeks out creative differences, things we have not seen before that evoke emotion. The most successful designers… Read More

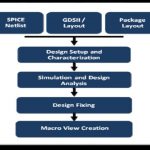

How to Spice Up Your Library Characterization

It used to be that at the mention of libraries, people would think of foundry PDK deliverables. However, now a host of factors such as automotive thermal requirements, nanometer FinFET processes, near threshold voltages, higher clock rates, high volumes, etc., have dramatically changed library development. These factors … Read More

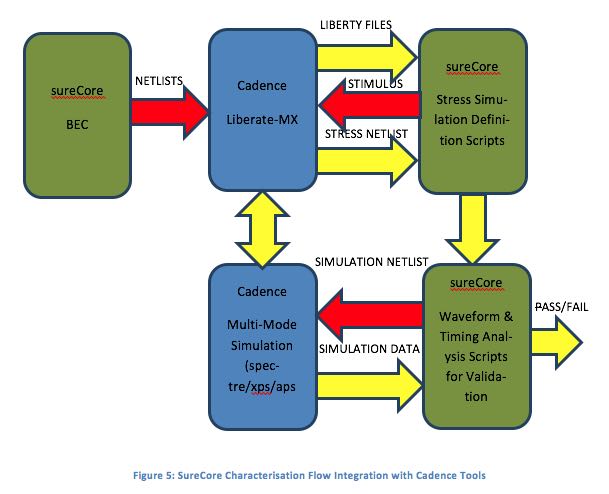

Low Power SRAM Complier and Characterization Enable IoT Applications

If you are designing an SOC for an IoT application and looking to minimize power consumption, there are a lot of choices. However, more often than not, looking at reducing SRAM power is a good place to start. SRAMs can consume up to 70% of an IC’s power. SureCore, a leading memory IP supplier, offers highly optimized SRAM instances … Read More

Improved Memory Design, Characterization and Verification

My IC design career started out with DRAM design, characterization and verification back in the 1970’s, so I vividly recall how much SPICE circuit simulation was involved, and how little automation we had back in the day, so we tended to cobble together our own scripts to help automate the process a bit. With each new process… Read More

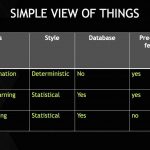

Machine Learning in EDA Flows – Solido DAC Panel

At DAC this year you could learn a lot about hardware design for AI or Machine Learning (ML) applications. We are all familiar with the massively parallel hardware being developed for autonomous vehicles, cloud computing, search engines and the like. This includes, for instance, hardware from Nvidia and others that enable ML … Read More

Challenges in IP Qualification with Rising Physical Data

With every new technology node, there are newer physical effects that need to be taken into account. And every new physical effect brings with itself several new formats to model them. Often a format is also associated with several of its derivatives, sometimes an standard reincarnation of a proprietary format further evolved… Read More

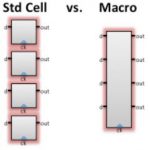

The Revenge of Microprocessor Design: The Return of the Macro

(Two Star Wars™ allusions in one title – eat your heart out George Lucas.) Most of us are comfortable with the idea that you design more or less whatever you want in RTL and let the synthesis tool pick logic gates to implement that functionality. Sure it may need a little guidance here and there but otherwise synthesis is more or less … Read More

Nine Cost Considerations to Keep IP Relevant

It’s about 15 years the concept of IP development and its usage took place. In the recent past the semiconductor industry witnessed start of a large number of IP companies across the globe. However, according to Gary Smith’s presentation before the start of 52[SUP]nd[/SUP] DAC, IP business is expected to remain stagnant for next… Read More

Xilinx & Apache Team up for FPGA Reliability at 20nm

In this age of SoCs with hundreds of IPs from different sources integrated together and working at high operating frequencies, FPGA designers are hard pressed keeping up the chip reliability from issues arising out of excessive static & dynamic IR drop, power & ground noise, electro migration and so on. While the IPs are… Read More