In the rapidly evolving landscape of artificial intelligence (AI) and data-intensive applications, the demand for high-performance interconnect technologies has never been more critical. Even the 100G Interconnect is already not fast enough for infrastructure applications. AI applications, with their massive datasets and complex algorithms, are driving the need for unprecedented data transfer speeds. The 224G Serializer/Deserializer (SerDes) stands at the forefront of the high-speed data communication revolution, ushering in a new era of unprecedented performance and adaptability.

Alphawave recognizes this market need and addresses it head-on with its cutting-edge 200G interconnect technologies. It is a testament to the company’s commitment to staying ahead of the data curve, empowering industries with the speed and efficiency needed to propel AI and high-performance computing into the future.

Recently, the company hosted a webinar on this topic and shared results from their AthenaCORE 224G SerDes TestChip. This post takes a look at Alphawave’s efforts toward unleashing the 1.6T ecosystem with its comprehensive offerings including its 200G interconnect technology.

Leveraging Alphawave’s 112G SerDes Success to Deliver Robust 224G SerDes

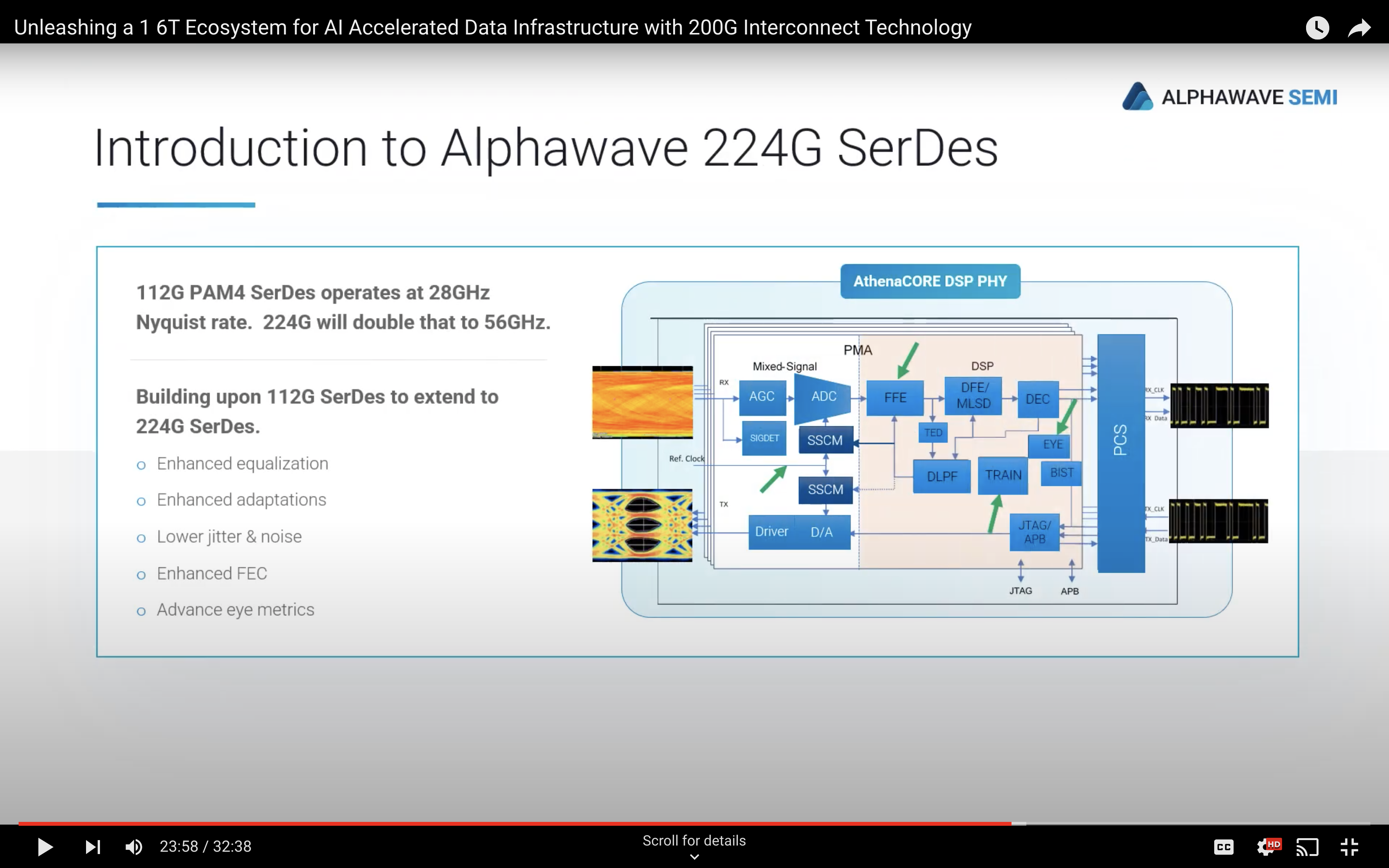

By extending its proven 112G SerDes to support a remarkable 224Gbps, Alphawave has not only doubled the data rate but has also unlocked new possibilities for data-intensive applications, particularly in the realm of Artificial Intelligence (AI) and advanced computing. Overcoming the associated challenges and complexities of 200G Interconnect called for a combination of advanced technologies, innovative design approaches, and collaborative efforts within the industry. Alphawave has built upon this 112G SerDes success to deliver the even more stringent requirements of a 224G SerDes.

The AlphaCORE DSP-based Serializer/Deserializer (SerDes) architecture is engineered to deliver versatile high-speed data communication solutions, featuring a configurable 112G Digital Signal Processor (DSP). The configurability of the DSP architecture enables adaptation for diverse applications and performance demands, providing a plug-and-play modular design for interchangeability and easy integration. Operating at a data rate of 112 gigabits per second (112G), the architecture aligns with the requirements of modern data communication in fields such as data centers, networking, and high-performance computing. With an emphasis on application-customized solutions, flexibility, and adaptability, the SerDes can be tailored to specific use cases, showcasing its ability to optimize performance for varying applications and environments. The inclusion of a DSP underscores its significance in tasks like equalization, error correction, and signal conditioning. Designed for ease of integration and adaptable to various Plug and Play Modules, the architecture ensures seamless compatibility with different components and functionalities. As a high-speed communication solution, the architecture meets the evolving demands of data rates and aligns with advancements in communication standards, making it well-suited for dynamic and future-oriented communication environments.

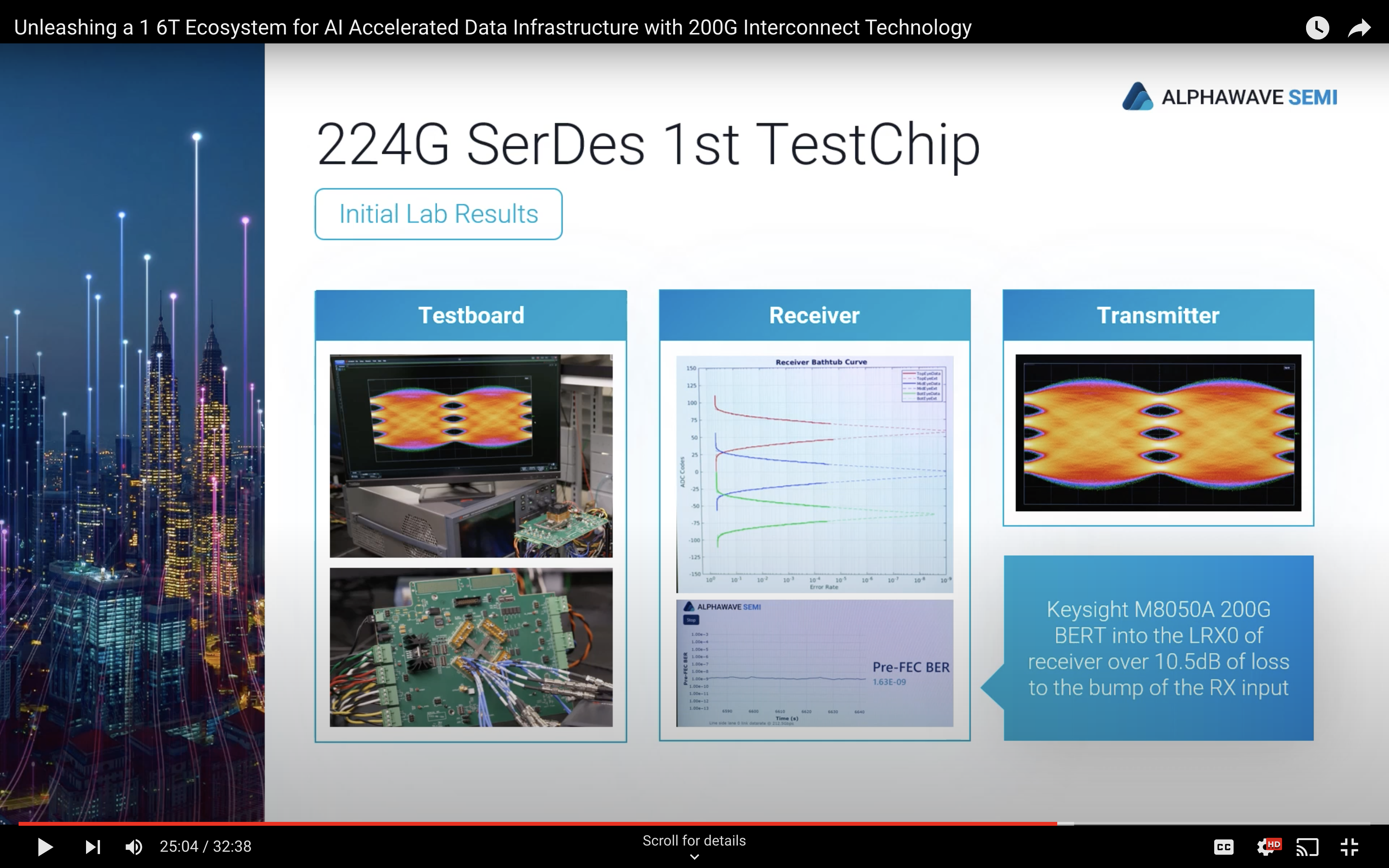

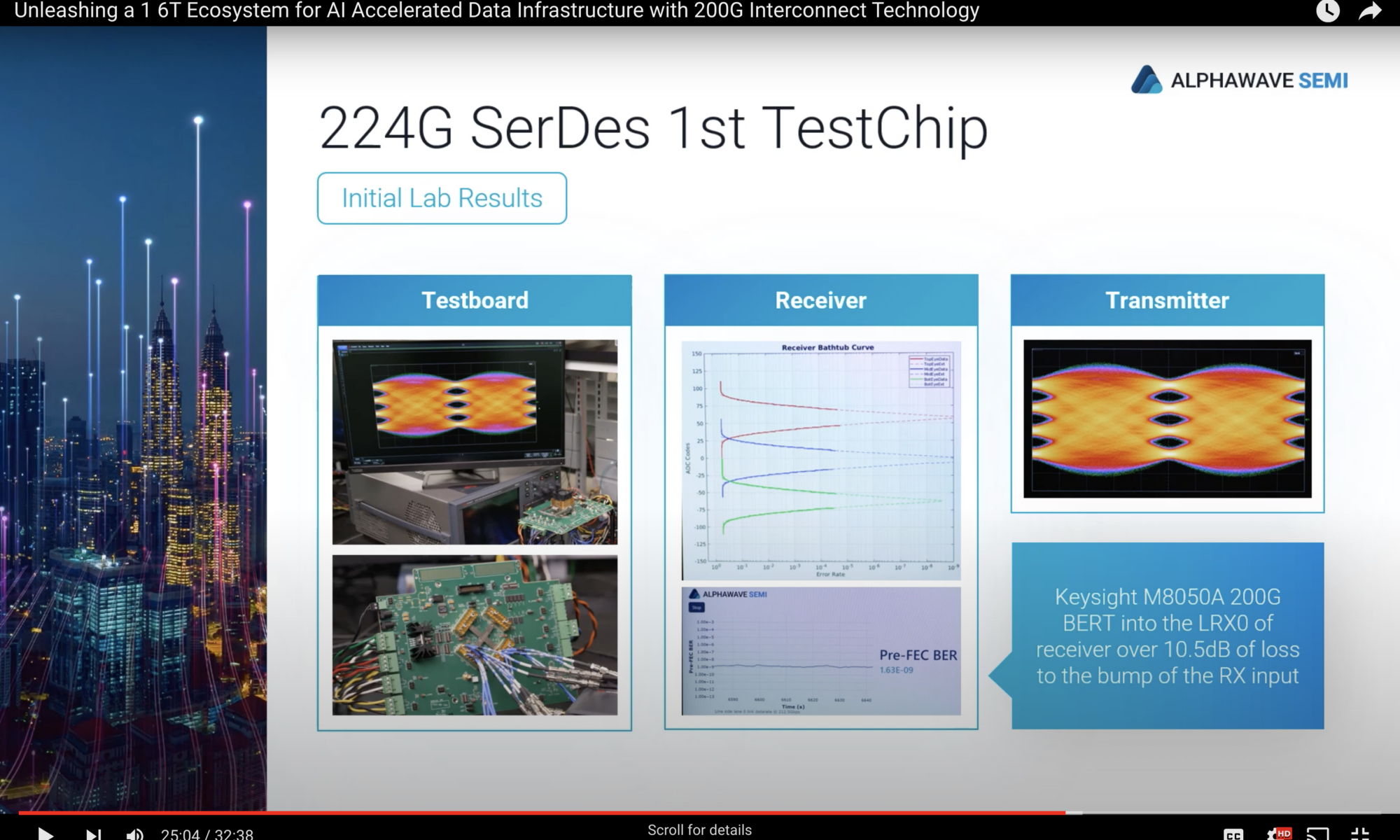

AthenaCORE 224G SerDes TestChip Results

Alphawave’s Innovative Development Efforts

Alphawave’s 200G interconnect technologies are not only about speed but also about efficiency and reliability. The 200G interconnect challenges include signal integrity issues, crosstalk, and dispersion. The company invests in advanced modulation schemes, such as PAM4 (Pulse Amplitude Modulation 4) which allows multiple bits to be encoded in a single symbol, effectively increasing the data rate. Alphawave also deploys advanced DSP techniques and adaptive error correction schemes to enhance the reliability and performance of data transmission at 200G speeds.

Advanced DSP Techniques

Maximum Likelihood Sequence Detectors (MLSD) represent a sophisticated Digital Signal Processing (DSP) technique employed in communication systems, notably effective in scenarios featuring intersymbol interference (ISI). Unlike conventional methods that aim to eliminate ISI, MLSD uniquely capitalizes on the energy within interference to boost signal power, optimizing symbol sequence detection. Its mathematically optimal approach involves an exhaustive search over all possible symbol sequences, minimizing mean square error to identify the transmitted sequence. Recognized for its capacity to significantly enhance system performance, MLSD is particularly applied in high-speed data communication and optical communication, addressing concerns related to signal distortion due to ISI. While MLSD’s computational demands raise complexity considerations, the technique’s adaptability to varying channel conditions underscores its efficacy in dynamic communication environments.

Forward Error Correction (FEC) Strategies

Alphawave embraces adaptive Forward Error Correction (FEC) strategies, allowing for dynamic adjustments based on real-time channel conditions. This flexibility ensures optimal performance without compromising on bandwidth efficiency. FEC empowers systems to establish higher Bit Error Rate (BER) targets on electrical links, providing a threshold for tolerating and correcting errors. Adaptive FEC dynamically adjusts error correction strength, balancing correction and bandwidth efficiency based on real-time channel conditions. The ascent of adaptive and dynamic FEC strategies enhances system adaptability, while integration with advanced modulation schemes optimizes performance, particularly in high-speed and optical communication systems.

Versatile Options to Support the 1.6T Ecosystem

Alphawave provides versatile options for switch ASICs (Application-Specific Integrated Circuits) in the 1.6T ecosystem. This includes the ability to stick with 512 × 100G links or leverage 256 x 200G links in a 1RU – 32 Port Switch configuration, offering scalability and flexibility for different deployment scenarios. The company’s UCle-enabled chiplets opens up new possibilities for chip-level modularity and scalability to address high-speed memory and compute requirements for infrastructure applications. With its 2.5D/3D packaging and application-optimized IP, the company navigates the delicate balance between complexity and performance to deliver advanced solutions.

Multi-Vendor Interoperability

Encouraging innovation, interoperability spans various dimensions, including form factors, SerDes interfaces, and management software, with the ultimate goal of achieving system compatibility. Multi-vendor Interoperability is a critical factor in the adoption and success of new technologies. Early adopters benefit from a broader range of compatible products, while downstream implementers leverage interoperability to streamline development, reducing time and costs. Setting performance standards, interoperability ensures users can anticipate how different components will function together in a system. This fosters quicker access to lower-cost technology, driven by competition in a diverse ecosystem of interoperable solutions.

Working with Standards Bodies

Alphawave understands the importance of multi-vendor interoperability and actively engages with industry standards bodies such as OIF (Optical Internetworking Forum) and IEEE 802.3 to contribute to the development of 200G signaling standards. This collaboration ensures interoperability and sets the stage for the seamless integration of Alphawave’s technologies into the broader ecosystem. Alphawave’s robust specifications and adherence to industry standards ensure that its 200G interconnect technologies seamlessly integrate with a variety of systems.

Summary

By actively contributing to industry standards, investing in advanced technologies, and providing versatile solutions, Alphawave is an important player in making the 1.6T ecosystem mainstream for the era of artificial intelligence. Alphawave offers a comprehensive suite of solutions designed for high-performance connectivity. Their High-Performance Connectivity IP spans across crucial areas like PCIe/CXL, Ethernet, and HBM/DDR, catering to the demands of high-speed data communications. The incorporation of chiplet technology, notably leveraging UCle, indicates a commitment to seamless chiplet interconnectivity. The specific chiplet types—IO, Memory, and Compute—underscore a modular approach, allowing different chiplets to function together harmoniously.

As data-intensive applications continue to evolve, Alphawave’s commitment to innovation positions it as a key enabler of the high-speed, reliable, and scalable AI data infrastructure of tomorrow. In essence, Alphawave is a key player in enabling flexibility, scalability and innovation for the upcoming 1.6T ecosystem.

To listen to the webinar, visit here.

Also Read:

Disaggregated Systems: Enabling Computing with UCIe Interconnect and Chiplets-Based Design

Interface IP in 2022: 22% YoY growth still data-centric driven

Alphawave Semi Visit at #60DAC

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.