The rapid expansion of data-intensive applications, such as artificial intelligence (AI), high-performance computing (HPC), and 5G, necessitates connectivity solutions capable of handling massive amounts of data with high efficiency and reliability. The advent of 224G/112G Serializer/Deserializer (SerDes) technology,… Read More

Tag: 112g

Unleashing the 1.6T Ecosystem: Alphawave Semi’s 200G Interconnect Technologies for Powering AI Data Infrastructure

In the rapidly evolving landscape of artificial intelligence (AI) and data-intensive applications, the demand for high-performance interconnect technologies has never been more critical. Even the 100G Interconnect is already not fast enough for infrastructure applications. AI applications, with their massive datasets… Read More

TSMC N3E is ready for designs, thanks to IP from Synopsys

TSMC has been offering foundry services since 1987, and their first 3nm node was called N3 and debuted in 2022; now they have an enhanced 3nm node dubbed N3E that has launched. Every new node then requires IP that is carefully designed, characterized and validated in silicon to ensure that the IP specifications are being met and … Read More

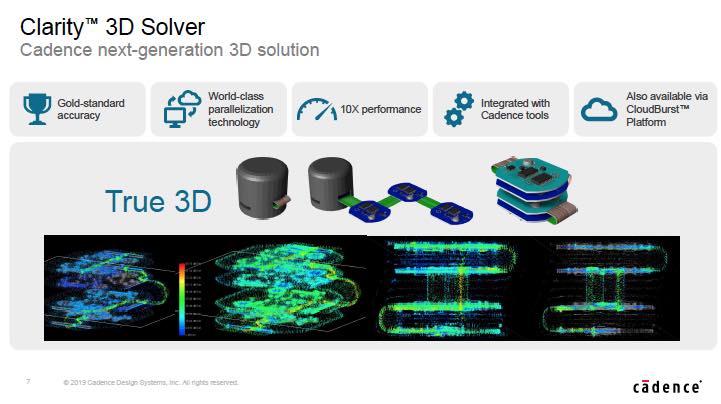

Solving the EM Solver Problem

The need for full wave EM solvers has been creeping into digital design for some time. Higher operating frequencies – like those found in 112G links, lower noise margins – caused by multi level signaling such as in PAM-4, and increasing design complexity – as seen in RDL structures, interposers, advanced connector… Read More

Getting to 56G Takes The Right Stuff

During the 1940s when aerospace engineers were attempting to break the sound barrier for the first time, they were confronting a slew of new technical issues that had never been dealt with before, and in some cases never seen before. In subsonic flight airflow was predictable and well understood. In crossing the sound barrier, … Read More

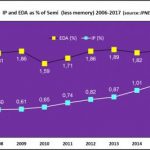

DAC 2019 Will Be Even More IP Friendly!

DAC 2019 will take place in Las Vegas (June 2-6) this year before moving back to San Francisco in 2020 and for the next 5 years. Considering the various rumors about merging the conference, or even the end of DAC, this is a very good news! Not only for Design Automation, but, as we will see, for the IP industry.

In fact, if we look at the exhibitor… Read More