Is it really a surprise if Qualcomm, the undisputed leader of Application Processor (AP) and BaseBand (BB) IC for wireless mobile, already one of the Arteris investors (with ARM, Synopsys, Docomo Capital and a bunch of VC), eventually acquires the best NoC IP technology (the technology, the engineering team and the rights, but not the company) available on the market? At first I would say “no” and I will summarize the two years history of blogs written about Network-on-Chip benefits here is Semiwiki. Then, if I wonder that Arteris has NOT been acquired by another IP vendor (ARM or Synopsys are both part of Arteris board), I realize that this acquisition by one of Arteris’ customer may raise some questions…

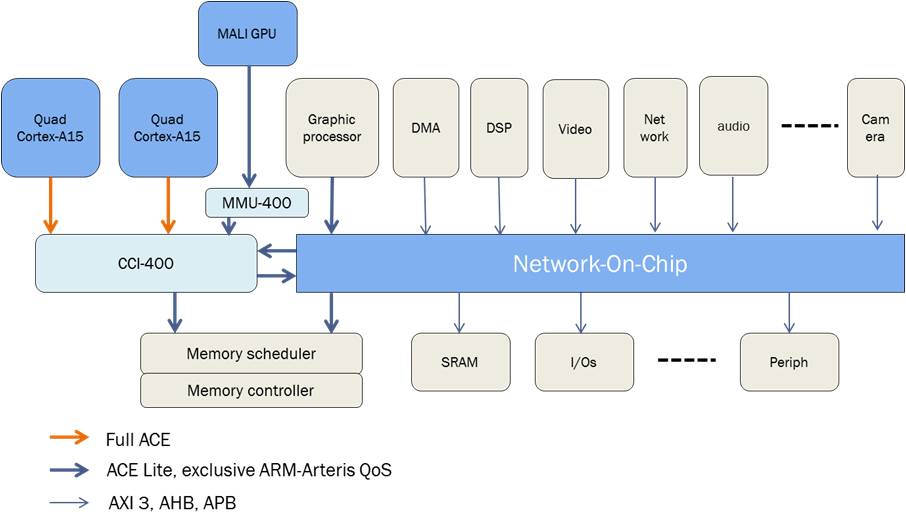

As written in my last blog about Arteris, “NoC packetize and serialize transaction address, control, and data information on the same wires, which allows transactions to be sent over smaller numbers of wires while maintaining high quality of service (QoS) for each transmission”… Integrating a NoC in a SoC will help solving several types of problems, at first related to back-end chip design.

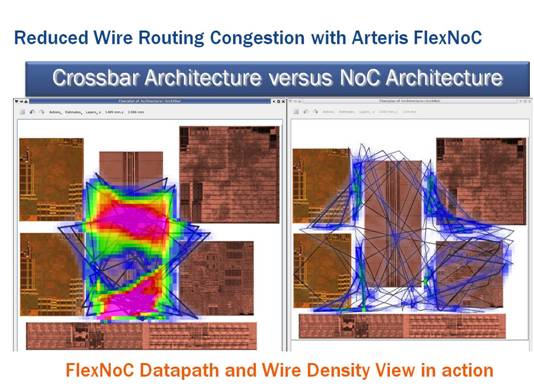

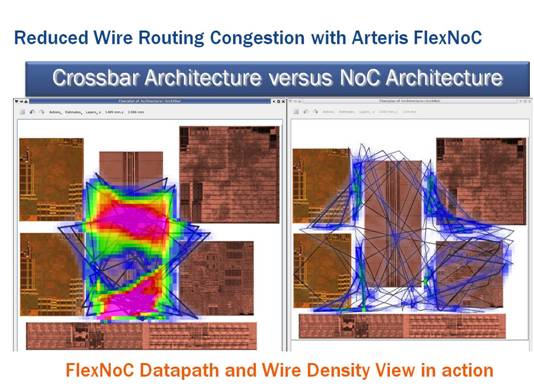

Chip designs frequently suffer from routing congestion, leading to increased die size and generating time to market delays. One of the first NoC related blog posted in Semiwiki deal about routing congestion issue, linked with Arteris “Routing Congestion” presentation. Implementing a NoC in a SoC clearly help reducing wire routing congestion, keep the die size in the target, and limit Place & Route (P&R) iterations.

The SoC design tend to integrate always more IP (according with Semico, on average, a Multimedia or AP SoC integrates today 80 blocks and almost 10 processor core). No surprise, as this trend is the result of Moore’s law, but this gate count inflation causes physical timing closure problems! These issues generate efficiency losses, bottlenecks, and squandered performance potential. The result can be directly perceived by the end user, degrading “user experience”, when the main processor is slower than expected, or the video exhibit poor quality. Implementing a NoC will greatly help reducing physical timing closure, allowing the chip maker extracting full benefit from the IP ha has paid for, and OEM launching the right product meeting market expectations. This is one of the reasons why Arteris has join in 2012 Inc 500 List of America’s Fastest-Growing Private Companies (Semiwiki blogged this), and got an ever better ranking in 2013 in Inc 500.

Thanks to the partnership between Carbon and Arteris, designers can run price, performance and area tradeoffs, the famous “PPA” optimization! Architects want to virtually prototype their design, as it can be a good way to run these PPA tradeoffs at early stages of the design, that they can do using Carbon’s SoCDesigner Plus, and prove their design assumptions before committing to the design implementation. “Our partnership with Arteris enables engineers to make architectural decisions and design tradeoffs based upon a 100%-accurate virtual representation,” states Bill Neifert, chief technology officer at Carbon Design Systems® in this post in Semiwiki.

If you consider this long list of benefits, reducing routing congestion (leading to smaller die size and faster Time To Market), allowing optimizing SoC architecture (reaching the best PPA tradeoff for the system) or help solving physical timing closure problems, you understand that a Fabless chip maker like Qualcomm will make the best use of Arteris NoC technology! But, some of the readers may argue that Qualcomm could just buy the NoC IP (that they did, by the way)…

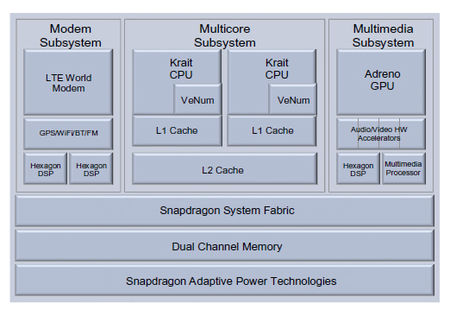

I think the answer is in Qualcomm product development strategy. Snapdragon AP SoC is based on Multi CPU core, ARM compatible CPU (Kraits). This means that Qualcomm has bought a technology license to ARM, allowing the company to modify ARM architecture to get the best PPA tradeoff and differentiate from competitors using the standard CPU IP from ARM, still staying compatible with ARM instruction set, as this is certainly a very strong requirement from Qualcomm’s customers. When doing GPU IP selection, a chip maker has more freedom than for the CPU. He may choose between ARM or Imagination Technologies, and a couple of GPU IP vendors, with no need to be “GPU vendor X” compatible. So, what did Qualcomm to differentiate? The company decided to acquire AMD’s mobile graphic unit (for $65 million in 2009), and develop their own GPU core, Adreno, integrated into their AP. I could take another example with QDSP, internally developed by Qualcomm to support LTE in Baseband IC, but I think that Qualcomm product development strategy is clearly based on differentiation, for cores processors (CPU, GPU, DSP).

Qualcomm is ready to pay a high price to build differentiation. Because the NoC IP became a very important piece of the SoC puzzle, right after CPU and GPU, and certainly before any of the peripheral IP, usually standard based (USB 3.0, HDMI or UFS to name a few), the NoC can be used to create differentiation. Qualcomm is buying Arteris NoC Technology, and more than just the function, the right to stay above competition, by developing Qualcomm specific NoC. If Qualcomm is the only to use this “Super-NoC”, Qualcomm competitors keeping the right using Arteris “standard” NoC, then the differentiation is created. Some people may wonder if a quarter of a Billion $ (so far this amount is only a rumor) is too high for the acquisition of a technology like NoC… in fact, only Qualcomm may care about such a high price! Let’s say that this is the cost for future differentiation, the “NoC of the fourth type” or the product that Qualcomm competitor will not be able to use…

If you remember the last article from Kurt Schuler, VP of Marketing with Arteris, Kurt said “As chips like application processors for mobile devices grow in complexity, area, and transistor count, the need for an advanced interconnect fabric becomes more urgent. Distributed cache coherent interconnect fabrics will be the fourth era in the history of interconnect technology.” No doubt that Qualcomm has the brain and engineering power to develop this “NoC of the fourth type”. Arteris has kept the right to modify the current FlexNoC version, in order to support existing customers, and also to develop this next Network-on-Chip generation, assuming the IP vendor can quickly rebuild an engineering team and define a new Network-on-Chip architecture.

Eric Esteve from IPNEST

More Articles by Eric Esteve …..

lang: en_US

Share this post via:

Comments

0 Replies to “Qualcomm Arteris deal”

You must register or log in to view/post comments.