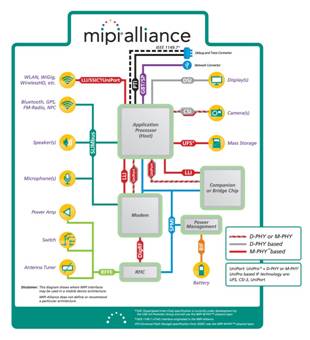

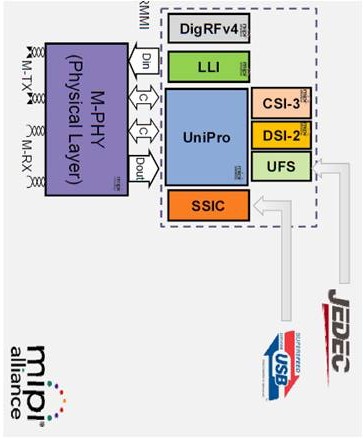

We have recently commented the announcement from MIPI Alliance and PCI-SIG, allowing PCI Express to be used in martphone, Media tablet and Ultrabook, while keeping decent power consumption, compatible with these mobile devices. The secret sauce is in the High Speed SerDes function selected to interface with these high data bandwidth protocol controller, like SuperSpeed USB Inter Chip (SSIC) from USB-IF, Universal Flash Storage from JEDEC and PCIe from PCI-SIG. The second PHY defined by MIPI Alliance: M-PHY, first specified in April 2011 at 1.25 Gbits/s, recently updated (June 2012) to run at 2.9 Gbits/s and a third generation coming next year will hit up to 5.8 Gbits/s.

You also may read the announcement from the MIPI Alliance: “MIPI® Alliance M-PHY® Physical Layer Gains Dominant Position for Mobile Device Applications”, and see the quote from Joel Huloux, MIPI Alliance Chairman at the end of this post…

In order for the information to be complete, the D-PHY (first PHY specification defined by the Alliance) was developed primarily to support camera and display applications, and is now widely used in the systems shipping now. But M-PHY is the function that should be integrated today to cope with the data bandwidth demand in the Gb/s range, and can be compared with SATA 6G or PCIe gen-2, but at lower power consumption. This is the key word for mobile application like smartphones and media tablet, this is exactly the feature which explains why ARM based Application Processor dominates the mobile systems, as strongly as X86 based chipset dominates the PC world-but not the mobile world. In fact, it would be very nice to have actual figures for the M-PHY power consumption, say ay 2.9 Gbit/s on a 28 nm (low power) technology node, and to compare it with PCI Express or USB 3.0 PHY at a similar speed and technology node. I am sure that this information is available “somewhere”, sharing it within the industry could be a good idea…

According with an analyst quoted in the PR from the MIPI Alliance “MIPI’s D-PHY interface is currently the dominant technology in mobile devices and we anticipate that its M-PHY interface will follow suit.” There is at least a good reason why D-PHY is dominant: if you remember, this function has been created to support Display and Camera interfaces. Display was relying on Low Voltage Differential Swing (LVDS) signaling, a pretty old technology, forcing to use wide parallel busses at the expense of real estate hungry connector, so a serial based solution like D-PHY and the Camera Interface Specification (CIS-2) was welcomed. Camera Controller IC interfaces with the Application Processor was varying with the chip supplier, not a comfortable situation for the wireless phone integrator, so Display Interface Specification (DSI) and D-PHY was also welcomed.

This explains why CSI-2 and DSI were among the first MIPI specifications to be widely adopted. But the Camera Controller chip makers, integrating the controller on the same IC than the image sensor, on a mature technology node like 90nm, may have some hard time integrating a multi-Gbit/s SerDes on such a technology. The story is slightly different for the Display controller chip, but I suspect the high voltage needed to drive the display to lead to the same situation: mature technology node are not high speed SerDes friendly! It may be that D-PHY will still be in use for some time, to support Display and camera Interfaces, and this is consistent with the feedback from IP vendors like Synopsys, still seeing demand for D-PHY in 28nm…

Now, we can come to the up-to-date M-PHY, which, as wisely noted by a cleaver analyst “…will follow suit”. To prepare the quote I have made for the MIPI Alliance in the M-PHY related PR, I have interviewed several IP vendors, as I thought their answer would be a good indication about how popular was the function. So, my question was “How many RFQ did you received (for M-PHY)?”, as I knew that asking about the number of design-in, or sales, would not be answered. As they knew that the answer may be published, let’s have a look at the respective answers from Synopsys, Mixel, Cosmic Circuits and Arteris.

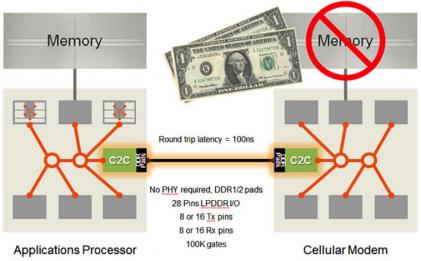

Arteris does not sell any PHY IP, but their Low Latency Interface IP has to be integrated with M-PHY. Arteris is claiming that LLI is used in ten projects, if you consider that the specification has been issued in February this year, that a pretty good adoption rate! Most probably, the fact that LLI allow sharing a single DRAM between AP and Modem, leading to save the cost of one DRAM, is a good enough incentive! Arteris perception of the market is that the AP chip makers prefer using in-house designed M-PHY, at least for the time being. Our perception is that the chip makers adopting LLI are probably the market leaders, and they have PHY dedicated design teams. This may change when the Tier-2 and 3 will also adopt LLI, according with Kurt Shuler, VP Marketing for Arteris.

This remark from Arteris makes the answer from Navraj Nandra, Director of Marketing for PHY IP products with Synopsys, even more interesting, as Synopsys claim to have had 120 RFQ for M-PHY. Let’s make it clear, a Request For Quotation (RFQ) does not mean that a product will be sold at the end. But that’s a good indication about the market behavior in respect with M-PHY.

I would like to thank Ganapathy Subramaniam, CEO of Cosmic Circuits, as he was the first to answer (during the week-end), and saying that the company has seen 10+ RFQ for the M-PHY. As far as I am concerned, my estimate would be that the M-PHY could generate up to 20 IP sales in 2012, but I may be optimistic, if we consider that many of the functions will come from internal sourcing…

The year 2013 could be very interesting to monitor, as numerous functions, like PCI Express, UFS, SSIC on top of the MIPI specific functions like LLI, DigRFV4, DSI-2 or CSI-3, could be integrated and leading to controller IP sales (for the above mentioned IP) and M-PHY IP sales. This could happen, not only for chips used in mobile systems, but also in the traditional PC and PC peripherals segments, as wisely noted by Brad Saunders, Chairman/Secretary of the USB 3.0 Promoters Group: “MIPI’s low-power physical layer technology makes it possible for the PC ecosystem to benefit from the SSIC chip-to-chip interface”.

Quote from MIPI Alliance Chairman: “M-PHY has truly become the de-facto standard for mobile device applications requiring a low-power, scalable solution,” said Joel Huloux, Chairman of the Board of MIPI Alliance. “We are pleased to join with our partners at JEDEC, USB IF, and PCI-SIG, and MIPI member companies, to advance solutions that push the envelope in interface technology.”

Eric Esteve – from IPNEST

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.