Kurt Shuler from Arteris has written a short but useful blog about the various high speed interface protocols currently used in the wireless handset (and smartphone) IP ecosystem. Arteris is well known for their flagship product, the Network-on-Chip (NoC), and the Mobile Application Processor market segment represent the first target for NoC: NoC is the IP which help increasing overall chip performance by optimizing internal interconnect, allows avoiding routing congestion during Place & Route and finally helps SoC design team integrating more quickly the tons of various functions, such an IP is more than welcome in such a competitive IC market segment! To make it clear, NoC is supporting interconnects inside the chip, when Kurt’s blog deals with the various functions used to interface the SoC with the other IC, still located inside the system (smartphone or media tablet). The blog provides a very useful summary, under the form of a table listing the various features of: MIPI HIS (High Speed Interface), USB HSIC (High Speed Inter-Chip), MIPI UniPro & UniPort, MIPI LLI (Low Latency Interface) and C2C (Chip-To-Chip Link).

We will come back later on the listed MIPI specifications and USB HSIC, but I would like to highlight the last two in the list: LLIand C2C.

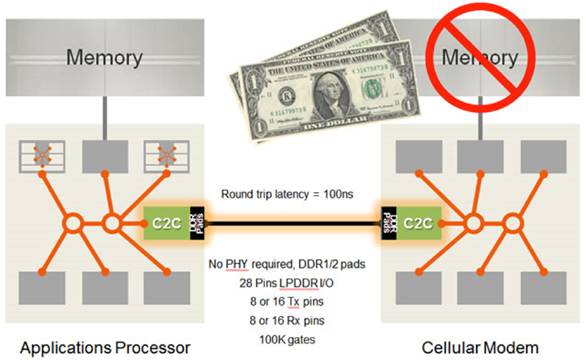

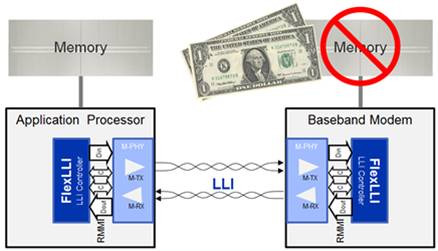

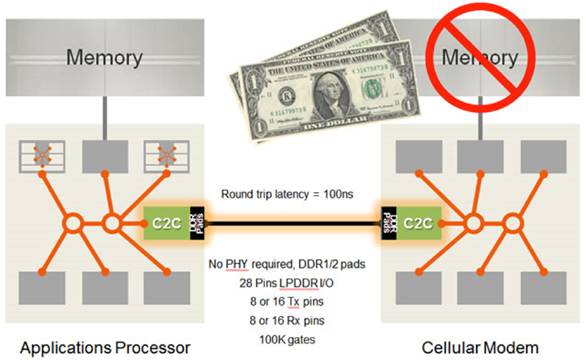

The first is based on high speed serial differential signaling and require using MIPI M-PHY physical block when the second is a parallel interface and requiring only LPDDR2 I /Os, but both functions are used in the aim of sharing a single memory (DRAM) between two chips, usually the application processor and the modem. The result is that the system integrator will save 2$ in the bill of material (BOM)… It does not look so fantastic, until you start multiplying these two bocks by the number of systems built by an OEM. Just multiply several dozens of million by 2$ and you realize that the return on investment (the additional cost of the C2C or LLI IP license) can come very fast, and represent several dozen of million dollar!

I should also add that Arteris is marketing these both controller IP functions, and if the company has the full rights on C2C, LLI is one of the numerous MIPI specifications. Just to give you some insight, LLI has been originally developed by one of the well known application processor chip makers, then the company has offered LLI to MIPI alliance and has asked Arteris to turn this internally developed function into a marketable IP, that Arteris is doing with an undisputable success. As far as I am concerned, I think that both LLI and C2C are “self selling”, as soon as you know that you can save $2 on the system BOM, you can imagine that OEM are pushing hard the chip makers to integrate such a wonderful function!

About Arteris

Arteris provides Network-on-Chip (NoC) interconnect semiconductor intellectual property (IP) to System on Chip (SoC) makers so they can reduce cycle time, increase margins, and easily add functionality. Arteris invented the industry’s first commercial network on chip (NoC) SoC interconnect IP solutionsand is the industry leader. Unlike traditional solutions, Arteris interconnect plug-and-play technology is flexible and efficient, allowing designers to optimize for throughput, power, latency and floorplan.

To know more about MIPI, you can visit:

MIPI Alliance web

MIPI wikion Semiwiki

MIPI surveyon IPNEST

Reminder: for Kurt’s blog, just go here!

Eric Esteve from IPNEST

Share this post via:

Comments

0 Replies to “Arteris evangelization High Speed Interfaces!”

You must register or log in to view/post comments.