jms_embedded

Active member

I am trying to find some order-of-magnitude estimates for the various steps in wafer fabs, and am wondering which are the biggest contributors to cycle time.

I've found various numbers for days per mask layer in published literature but they're generally in the 1-2 DPML range, and with X-factors in the 3-5 range that puts the raw processing time per layer somewhere in the 5-16 hour range, with queueing time making up the rest.

I've found various product brief / press releases from equipment manufacturers like ASML, Nikon, AMAT, Lam Research, etc. for DUV/EUV scanners, chemical vapor deposition tools, etchers, inspection machines, etc. and they're all in the 50 - 300 WPH range for throughput, but no numbers on latency. (example: even if the fastest scanners are 300WPH = 12 seconds per wafer, maybe the wafer has to wait for the entire lot before it can move on to the next process step, which means 12 s * 25 = 5 minutes per lot... but even if there are 5 lots waiting in a queue behind it, that's only 25 minutes which is small compared to the total raw processing time.)

What about ion implantation / diffusion furnaces? Do these take longer? (I'm assuming diffusion furnaces might take several hours just due to the slow nature of heating/cooling and the need to avoid rapid thermal shock.) If so, do they contribute the most to raw process time and/or queueing time?

If anyone has some references they could point me at, I would appreciate it. (I suspect none of the IDMs/foundries publish their numbers, but someone must have a rough order of magnitude in a book or article somewhere)

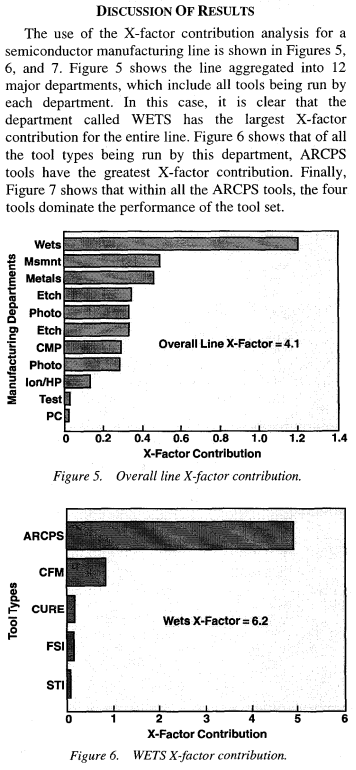

The only tangible hints I found were in a 1998 article by Donald Martin from IBM (https://ieeexplore.ieee.org/document/731385) which mention "a six-hour furnace operation" and "20-minute ion implant" as hypothetical examples (and later another hypothetical furnace step with "a raw process time of four hours") and this section on major contribution to X-factor, where "WETS" perhaps = wet bench.

I've found various numbers for days per mask layer in published literature but they're generally in the 1-2 DPML range, and with X-factors in the 3-5 range that puts the raw processing time per layer somewhere in the 5-16 hour range, with queueing time making up the rest.

I've found various product brief / press releases from equipment manufacturers like ASML, Nikon, AMAT, Lam Research, etc. for DUV/EUV scanners, chemical vapor deposition tools, etchers, inspection machines, etc. and they're all in the 50 - 300 WPH range for throughput, but no numbers on latency. (example: even if the fastest scanners are 300WPH = 12 seconds per wafer, maybe the wafer has to wait for the entire lot before it can move on to the next process step, which means 12 s * 25 = 5 minutes per lot... but even if there are 5 lots waiting in a queue behind it, that's only 25 minutes which is small compared to the total raw processing time.)

What about ion implantation / diffusion furnaces? Do these take longer? (I'm assuming diffusion furnaces might take several hours just due to the slow nature of heating/cooling and the need to avoid rapid thermal shock.) If so, do they contribute the most to raw process time and/or queueing time?

If anyone has some references they could point me at, I would appreciate it. (I suspect none of the IDMs/foundries publish their numbers, but someone must have a rough order of magnitude in a book or article somewhere)

The only tangible hints I found were in a 1998 article by Donald Martin from IBM (https://ieeexplore.ieee.org/document/731385) which mention "a six-hour furnace operation" and "20-minute ion implant" as hypothetical examples (and later another hypothetical furnace step with "a raw process time of four hours") and this section on major contribution to X-factor, where "WETS" perhaps = wet bench.