Huawei Tests Brute-Force Method for Making More Advanced Chips

(Bloomberg) -- Huawei Technologies Co. and a secretive chipmaking partner in China have filed patents for a low-tech but potentially effective way to make advanced semiconductors, raising the prospect that China could improve chip production techniques despite US efforts to halt its progress.

The companies are developing technologies that involve self-aligned quadruple patterning, or SAQP, and should reduce their reliance on high-end lithography, according to patent filings to the Chinese intellectual property authority. That may allow them to produce advanced chips without ASML Holding NV’s state-of-the-art extreme ultraviolet lithography equipment. Netherlands-based ASML, the sole provider of EUV machines, cannot sell them into China because of export controls.

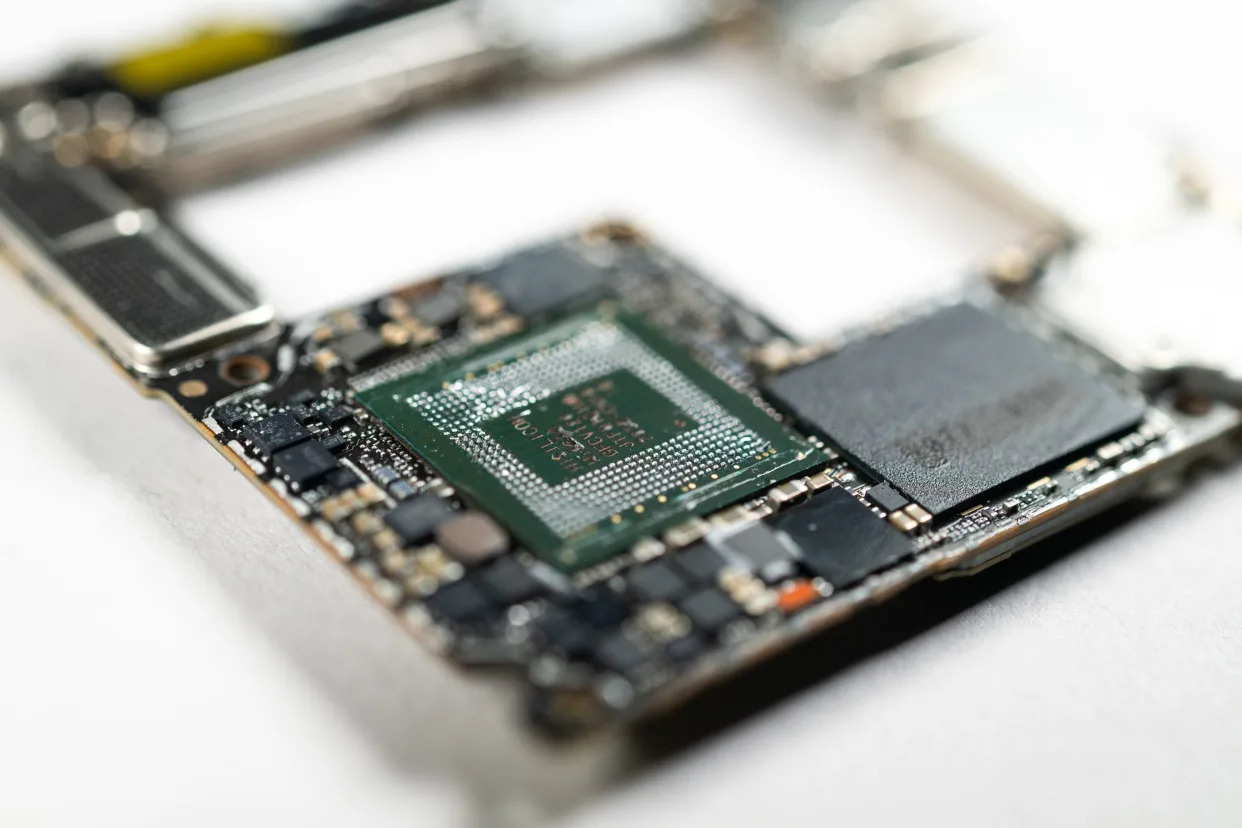

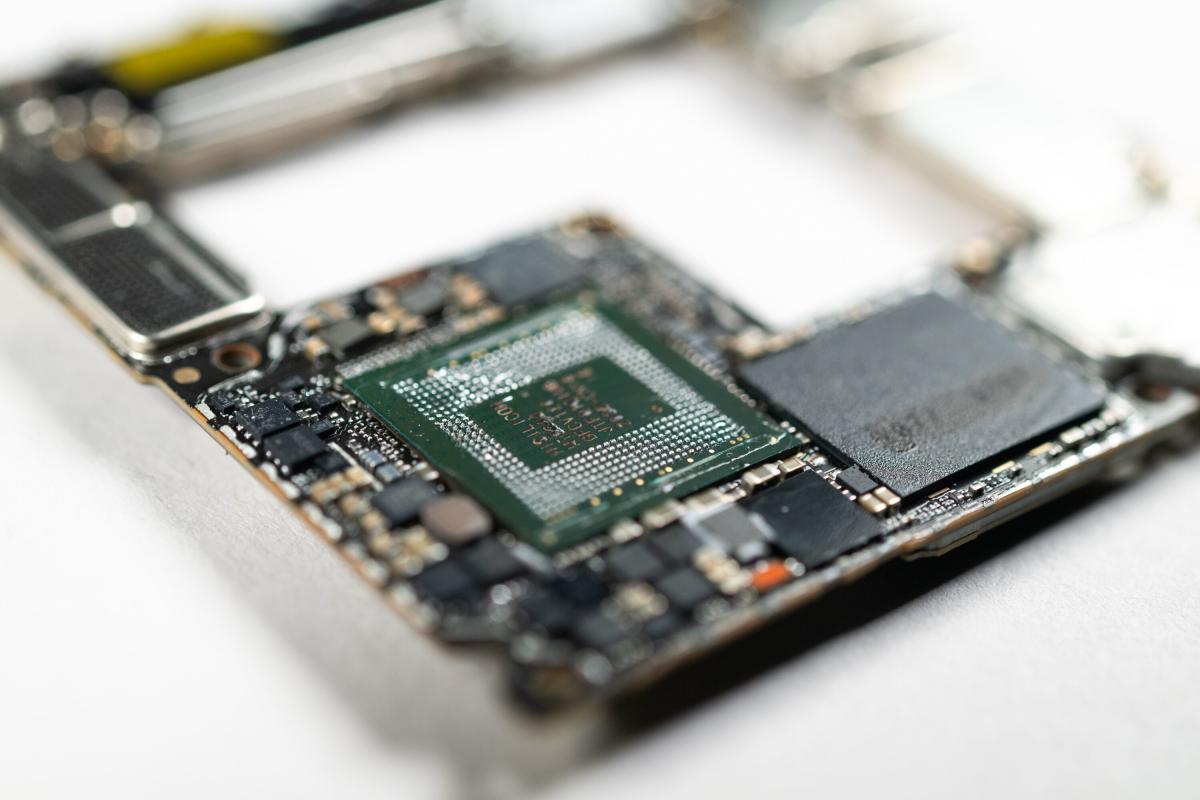

Quadruple patterning is a technique for etching lines on silicon wafers multiple times to increase transistor density — and therefore performance. Huawei’s patent application, released on Friday, describes a method that uses the technology to make more sophisticated semiconductors. “Adoption of this patent will increase the design freedom of circuit patterns,” said the filing to China National Intellectual Property Administration.

SiCarrier, a state-backed chipmaking gear developer that works with Huawei, was granted a patent that involves SAQP, in late 2023. Its patent employs deep ultraviolet lithography, or DUV, chipmaking machines and the SAQP technology to achieve certain technical thresholds seen on 5 nanometer chips, according to its filing. The practice can avoid the use of EUV machines while reducing manufacturing cost, it said.

Quadruple-patterning technology is good enough for China to make chips at 5nm, but China still needs to get its hands on EUV machines in the long run, according to Dan Hutcheson, vice-chairman at research firm TechInsights. “It can mitigate them, but not completely overcome the technical issues of not having EUV,” he said.

Leading chipmakers like Taiwan Semiconductor Manufacturing Corp. use EUV machines to produce advanced chips because they have the highest production yields — meaning the cost per chip is minimized. If Huawei and its partners use alternative methods for semiconductor production, their cost per chip may be higher than the industry’s standards.

The most advanced chips now in commercial production use 3nm technology, including chips that TSMC makes for the likes of Apple Inc. China is currently capable of making 7nm chips, two generations behind, but advancing to 5nm would put it only a single generation behind the global leaders.

The US and its allies have been tightening China’s access to semiconductors and chipmaking equipment for years, with the Biden administration arguing such controls are necessary for national security. That includes bans on the export of ASML’s EUV chipmaking machines and Nvidia Corp.’s most powerful graphic processors, used for training artificial intelligence services.

But Chinese companies are investing billions to develop their domestic chip capabilities and Huawei unveiled a breakthrough smartphone last year that was powered by an advanced 7nm processor. That suggested the country’s tech sector is making progress despite the efforts of the US, the Netherlands and Japan.

In response, the Biden administration is looking for additional means to contain China’s progress. It’s pressing allies like South Korea and Germany to join the effort, and is considering blacklisting even more Chinese chip firms linked to Huawei, including SiCarrier.

A cohort of Chinese chip equipment makers including Naura Technology Group Co. and Advanced Micro-Fabrication Equipment Inc., are also looking into complementing multiple patterning technology with etching systems to produce 7nm or more advanced chips because EUVs are out of reach, according to a memo authored by Citigroup’s analysts including Jamie Wang and Kevin Chen.

“Chinese semiconductor companies mainly resort to SAQP to produce advanced chips, which could increase the density of etching machines in China,” it said.

Beijing this year has thrown its backing fully behind the nation’s most prominent suppliers of chipmaking gear. This month, Premier Li Qiang visited the offices of Naura Technology in a widely publicized personal tour, usually orchestrated to signal central government support.

Huawei Tests Brute-Force Method for Making More Advanced Chips

(Bloomberg) -- Huawei Technologies Co. and a secretive chipmaking partner in China have filed patents for a low-tech but potentially effective way to make advanced semiconductors, raising the prospect that China could improve chip production techniques despite US efforts to halt its...