For decades now I’ve watched the incredible growth of SoCs in terms of die size, transistor count, frequency and complexity. Instead of placing all of the system complexity into a single, monolithic chip, there are now compelling reasons to use a multi-chip approach, like when the maximum die size limit is reached, or it’s more cost effective to use two or more smaller chiplets designed in a variety of technology nodes. Taking the multi-die system path introduces new chiplet interconnect challenges:

- Reliable connectivity

- High bandwidth

- Low power

- Low latency

- Standards support

Fortunately for the industry there’s been a collective effort to develop standards, and the Universal Chiplet Interconnect Express™ (UCIe™) has gained traction by enabling package-level integration through a die-to-die interconnect along with a connectivity protocol, so that multiple vendors can grow an ecosystem through interoperability. UCIe covers three stack layers, and the PHY layer defines the electrical interface.

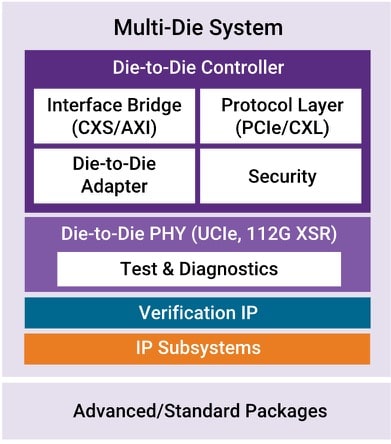

Synopsys has been delivering IP for many years now across many domains, like: Interface, Foundation, Processor, Security, Analog, Subsystems. They’ve also joined the UCIe Consortium, contributing to the specification of the standard. There’s a UCIe PHY IP from Synopsys, along with a UCIe Controller IP and verification IP.

In March 2023 Synopsys announced that their UCIe PHY IP had a tape-out on the TSMC N3E process node.

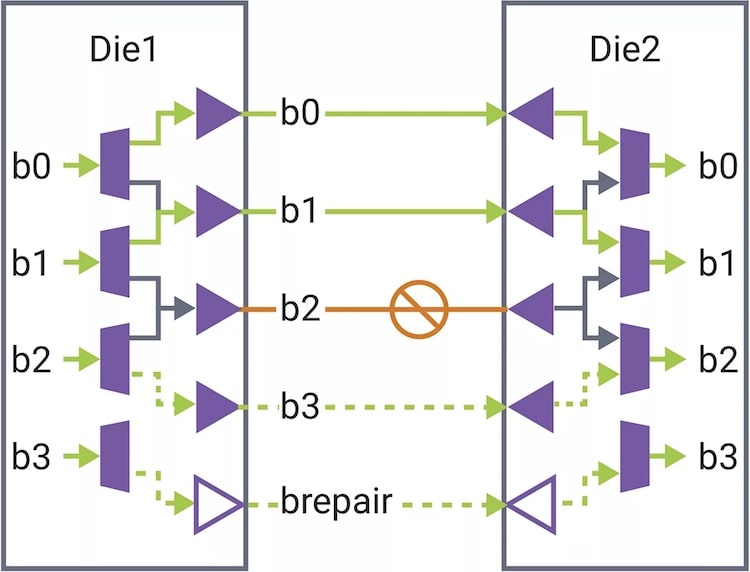

For reliable connectivity the UCIe standard has up to 8 spare pins per direction, allowing repair of the functional links.

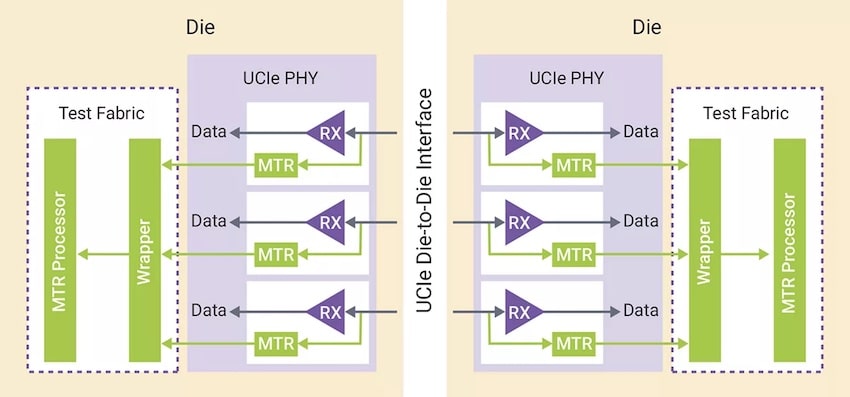

Variations in the die-to-die interface signals are monitored by Signal Integrity Monitors (SIM), then the Monitoring, Test and Repair controller can determine the health of the multi-die system for predictive maintenance of the links. Synopsys has the Silicon Lifecycle Management tools to monitor the UCIe interface while its operating, detecting soft or hard errors.

Bandwidth for UCIe using the Synopsys PHY IP is up to 5Tbps/mm efficiency. The Controller IP supports streaming protocols as well as PCI Express and CXL protocols, delivering secure, low-latency data.

Coming up to speed on the UCIe specification takes precious engineering time, so re-using protocol verification IP is going to save your team valuable time to market. Verification IP running on a software simulator provides a good start, then adding hardware emulation with Synopsys ZeBu and prototyping with Synopsys HAPS Platform offer more time savings to debug the whole system running software.

Routing the UCIe signals between dies is automated by the Synopsys 3DIC Compiler tool, and it works for 2.5D chiplets.

Summary

Systems engineers today still have to decide between two approaches for implementation, the traditional single-chip SoC, or the multi-die system. EDA vendors like Synopsys have long been automating the EDA tasks for a single-chip SoC, and they’ve also extended their automation into the realm of 2.5D by developing new EDA tools, verification and IP for multi-die systems.

The interconnect challenges of multi-die systems have been addressed through standardization efforts like UCIe, which lowers the risks for new projects considering chiplet-based systems. Synopsys is one of the few EDA and IP vendors with such broad support of multi-die systems.

Related Blogs

- Chiplet Q&A with Henry Sheng of Synopsys

- Multi-Die Systems: The Biggest Disruption in Computing for Years

- Takeaways from SNUG 2023

- Multi-Die Systems Key to Next Wave of Systems Innovations

- UCIe Specification Streamlines Multi-Die System Design with Chiplets

- Getting to Faster Closure through AI/ML, DVCon Keynote

- Upcoming Webinar: 3DIC Design from Concept to Silicon

- Heterogeneous Integration – A Cost Analysis

- Why Optimizing 3DIC Designs Calls for a New Approach

Comments

There are no comments yet.

You must register or log in to view/post comments.