Integration is often an underrated attribute of good tools, compared to raw performance and technology. But these days integration is differentiation (try telling that to your calculus teacher). Today at DVCon Synopsys announced Verification Compiler which integrates pretty much all of Synopsys’s verification technologies (including the technology acquired in the SpringSoft acquisition) into a single tool. Verification Compiler is a complete portfolio of integrated, next-generation verification technologies that include advanced debug, static and formal verification, simulation, verification IP and coverage closure. Together these technologies offer a 5X performance improvement and a substantial increase in debug efficiency, enabling SoC design and verification teams to create a complete functional verification flow with a single product.

Integration is often an underrated attribute of good tools, compared to raw performance and technology. But these days integration is differentiation (try telling that to your calculus teacher). Today at DVCon Synopsys announced Verification Compiler which integrates pretty much all of Synopsys’s verification technologies (including the technology acquired in the SpringSoft acquisition) into a single tool. Verification Compiler is a complete portfolio of integrated, next-generation verification technologies that include advanced debug, static and formal verification, simulation, verification IP and coverage closure. Together these technologies offer a 5X performance improvement and a substantial increase in debug efficiency, enabling SoC design and verification teams to create a complete functional verification flow with a single product.

Existing methodologies using disparate tools are not very efficient, involving, as they do, duplicate steps, incompatible databases, multiple debug environments, inconsistent coverage metrics which all impact ease-of-use and productivity. And not in a good way.

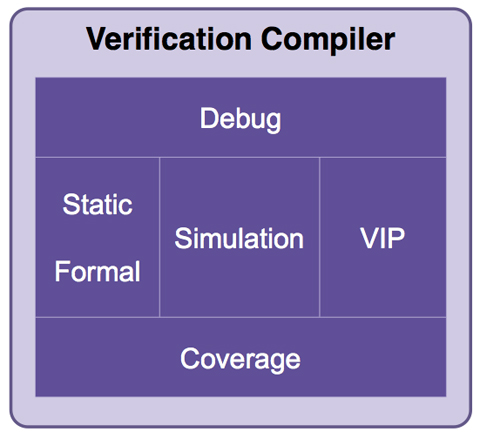

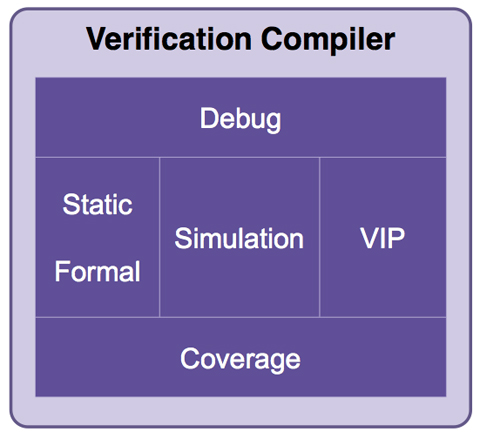

Verification compiler ties together the big pieces of verification: static and formal verification, simulation, VIP, debug and coverage. The goal is to “shift left” and find more problems earlier in the design cycle and achieve coverage goals earlier.

Under the hood there is a huge amount of raw technology in the various engines, and then the uniform way of accessing it, debugging it and sharing data means that it is easy to use and the performance of the engines is not lost in translation and other inefficiencies. Verification Compiler really is a single product with native interfaces and consistent databases.

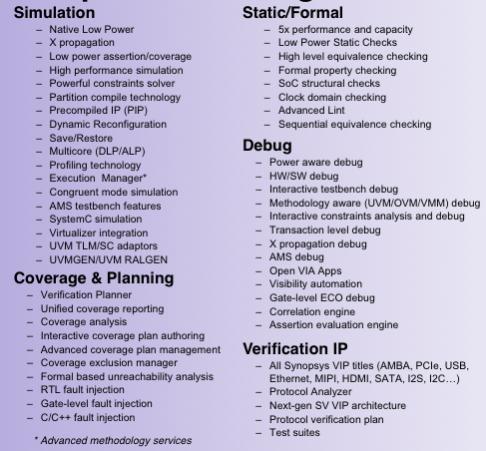

There is more than just integration of existing Synopsys technology. Probably the biggest new raw technology is that the formal analysis has been completely rebuilt from scratch with a lot more power, more performance and more capacity, an increase of 3-5X with full support for low power and clock domains.

There are big changes in debug too, focused on the challenges of large SoC development which has a large software component: interactive testbench debug, transaction debug, accelerated time to waveform for Zebu, AMS debug, power-aware debug, HW/SW debug. All with a common user-interface, way of displaying waveforms etc.

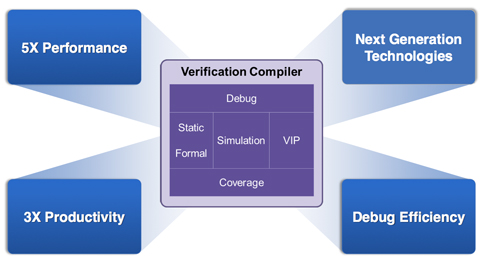

So how big a difference does this all make? Overall, a 5X performance increase (of course it is design dependent, ymmv, in some cases much more, occasionally less).

- 3-5X improvement on static and formal verification

- 4X on constraint runtime during simulation

- 10X+ compile turnaround time with partition compile

- 2X native power simulation

- 2X faster verification IP

- 2X with native FSDB

- 4X with native Siloti

In addition to raw performance increase, Synopsys and their early partners reckon an increase of 3X in productivity due to concurrent verification, automated setup, and integrated flows and methodology. The concurrent verification methodology is supported by the licensing approach Synopsys have taken. One Verification Compiler license actually gives you three keys so you (or your team) can concurrently run static/formal, simulation, and debug. All from a single license key. The component parts are also available for separate licensing (so you can still, for example, have lots of VCS licenses for regressions).

So in summary:

- Next-generation verification technologies, including static and formal verification, provide 5X performance improvement

- Native integration of simulation, static and formal verification, VIP) debug, and coverage technologies into a single product boosts performance and productivity

- New advanced SoC debug capabilities built on the easy-to-use Verdi[SUP]3[/SUP] debug platform enhance debug efficiency

- Complete low power verification with native low power simulation, X-propagation simulation, next generation low power static checking and low power formal verification

- A broad portfolio of VIP AMBA, Ethernet, MIPI, PCIe and more, integrated with simulation and debug for highest performance and productivity

- Concurrent verification licensing enables 3X productivity improvement overall

Verification Compiler is in limited customer availability and will be in full release in Q4.

Much more detail on the Synopsys website here.

More articles by Paul McLellan…

Comments

0 Replies to “Synopsys Announces Verification Compiler”

You must register or log in to view/post comments.