The HSPICE circuit simulator has been around for decades and is widely used by IC designers worldwide, so I watched the HSPICE SIG by video today and summarize what happened. Engineers from Micron, Altera and AMD presented on how they are using HSPICE to model TSVs, IBiS-AMI models and SERDES, respectively.

First up was Hany Elhak, the Product Marketing Manager, who thanked the many EDA sponsors from the HSPICE Integrators Program:

Micron

Fuad Badrieh from Micron talked on, Electrical Modeling of Through-Silicon Vias Using HSPICE.

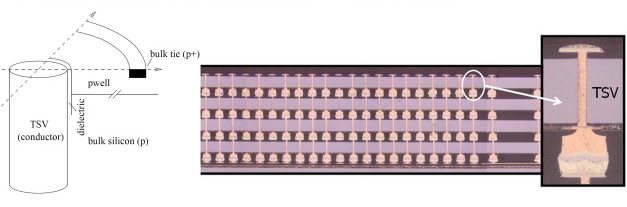

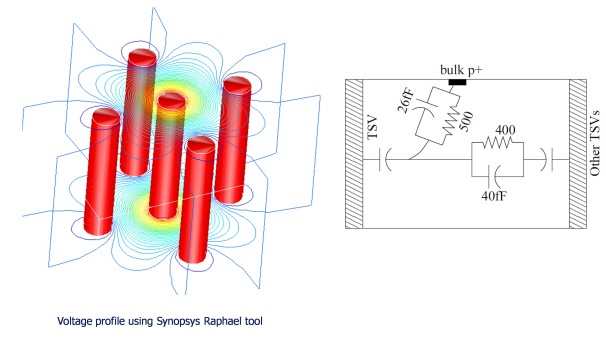

3D stacking holds promise for higher levels of system integration, and Through Silicon Vias (TSV) are one way to make these connections between multiple die. An accurate SPICE TSV model is required to simulate the interconnect parasitics properly. These TSVs are electrically isolated with oxide.

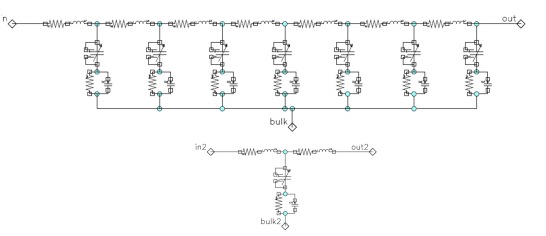

A SPICE model needs to include series resistance, inductance and skin effects which are voltage-dependent:

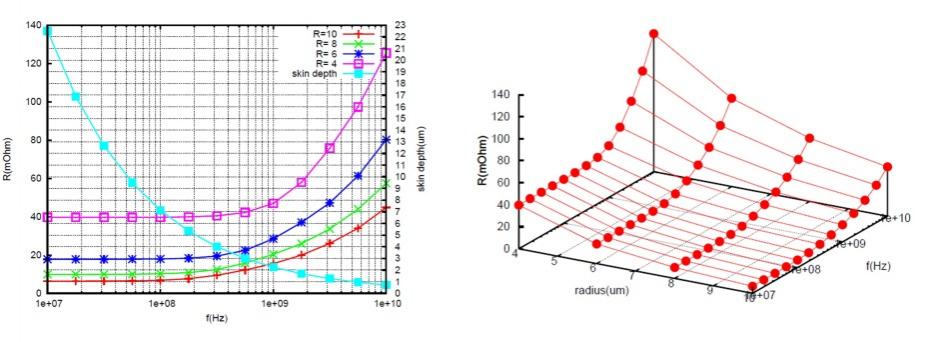

The TSV resistance is frequency and radius dependent (about 10 mili-Ohms):

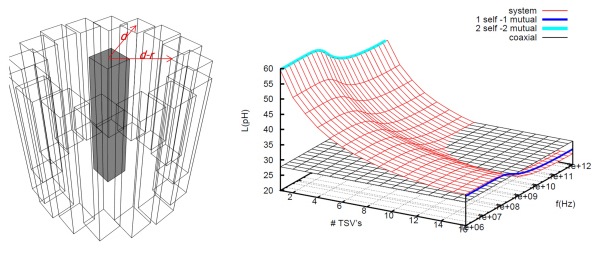

TSV loop inductance is complex because of how a TSV is surrounded by other TSVs and the bulk (about 40pH):

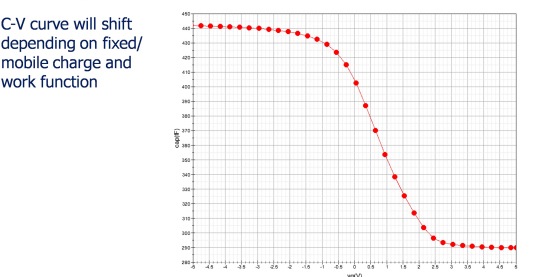

TSV capacitance is voltage dependent:

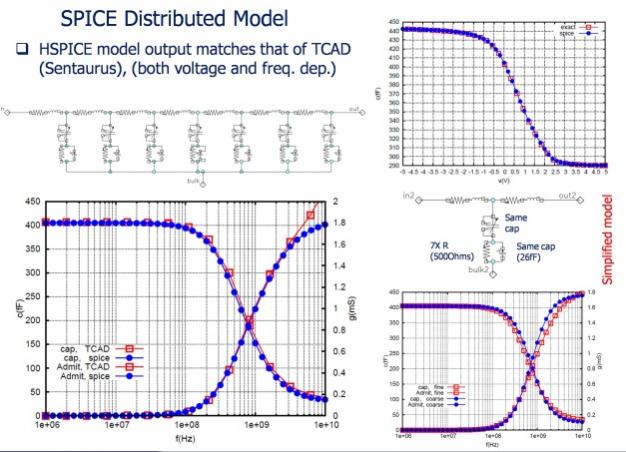

Taking all of these concepts together a SPICE distributed model is created and compared with TCAD tools (Sentarus):

The SPICE (blue lines) distributed model correlates quite well with the TCAD (red lines) model.

More work is required to capture a multi-port model of a TSV:

Micron has successfully created both a simple lumped and distributed models for TSVs that accurately simulate up to 10GHz for their stacked DRAM designs.

Altera

From Altera was David Banas speaking about, Using IBIS-AMI Models Effectively in HSPICE.

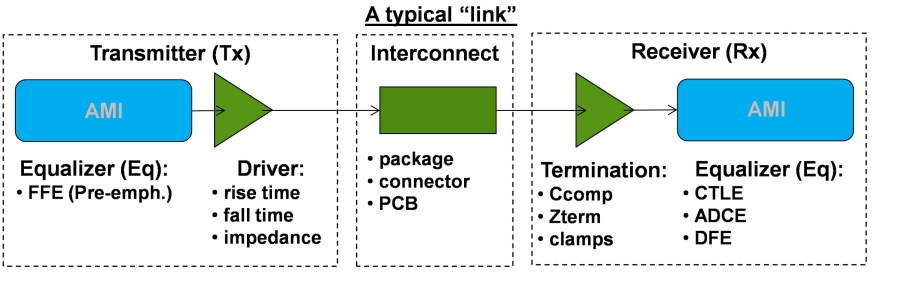

What is an IBIS-AMI Model? It’s a black box, behavioral model of the Rx (receiver) and Tx (transmitter) ends of a serial channel. Users of IBIS-AMI models get a binary file that protects the IP, and simulates fast.

The Green parts model the channel and can use standard IBIS models, the blue parts use the IBIS-AMI model. The circuit simulator reads the models and does its convolution. The IBIS-AMI models are not like time step-based models, instead they are adaptive while simulating very fast which enables high bit error rate simulations. The IP for equalization is totally protected with IBIS-AMI models.

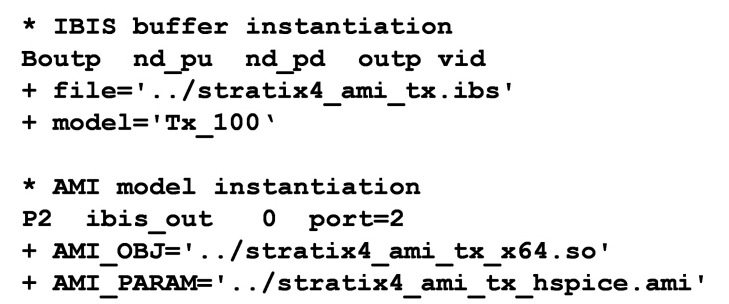

Only use IBIS-AMI models for .STATEYE analysis, not .TRAN analysis. Your netlist with IBIS-AMI is familiar to a standard HSPICE netlist with IBIS:

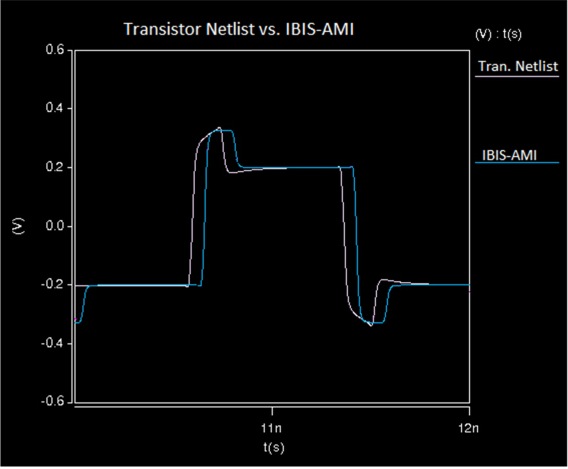

Why use HSPICE to simulate an IBIS-AMI model? Accuracy, speed and it’s easy to use. A simulation comparison between a transistor-level netlist (red color) and IBIS-AMI (blue color) is shown below:

AMD

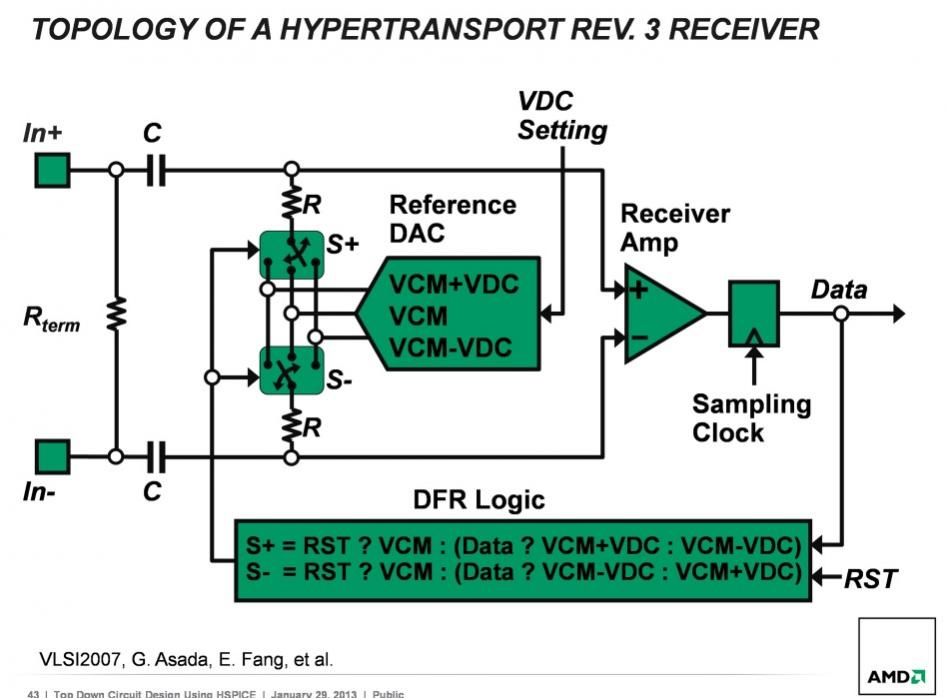

On the microprocessor side was Gladney Asada from AMD talking on, Top-Down Circuit Design Using HSPICE. SERDES is used to provide high speed serial communications (PCI Express, GDDR5, DDR, Serial ATA, USB, HyperTransport, DisplayPort, HDMI, DVI) on CPU and GPU chips.

Starting with the specs a circuit topology is decided, Verilog-A models created, HSPICE is used to characterize, IC layout is created, and finally a verification testbench is used. When a new SERDES spec comes out we have to decide if a previous IP can be re-used, or if a new topology is required.

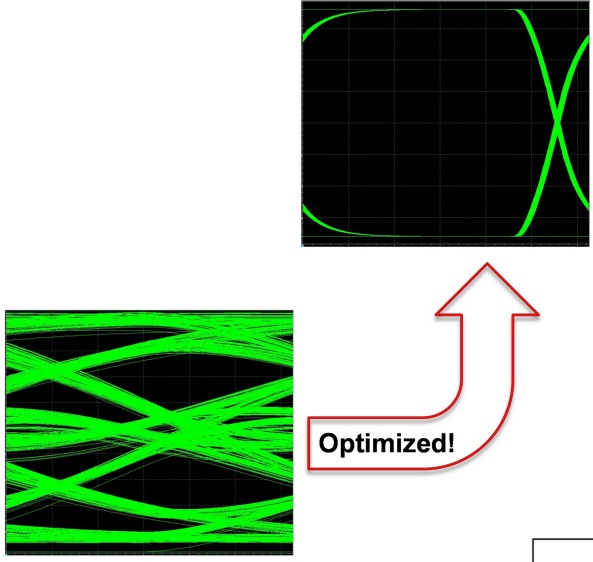

From a topology the Verilog-A models were then created for each design component and a HSPICE netlist was created with Verilog-A instances. HSPICE is run and the design is tuned until the eye results are optimized.

Synopsys

Finally, Scott Wedge from Synopsys concluded by covering the 32 year history of HSPICE.

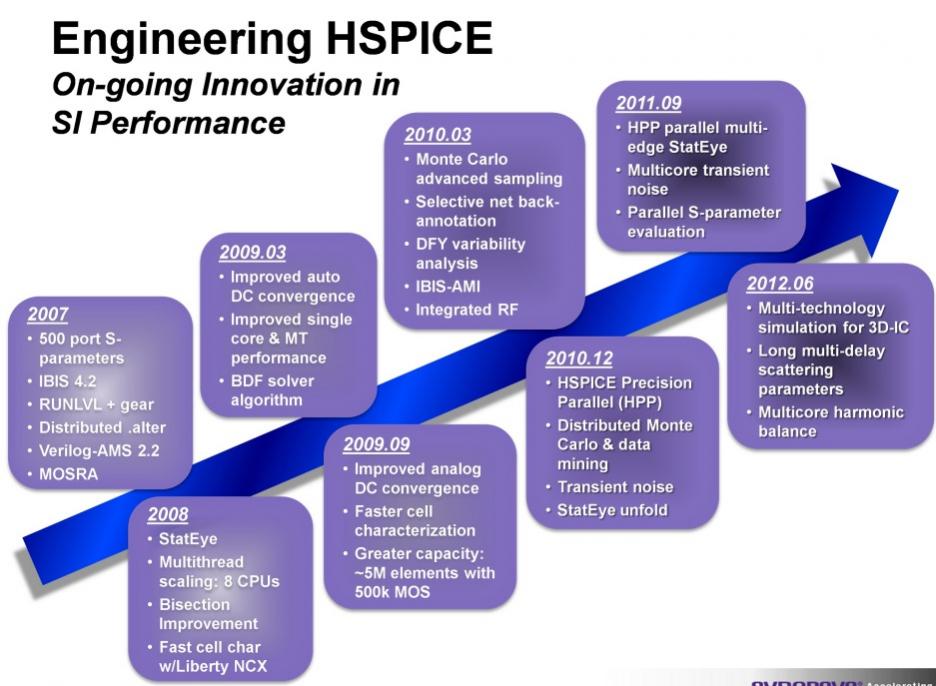

Lots of new features added over the years:

Simulating on up to 16 cores gets about 10X simulation speed up in HSPICE now, it’s called Precision Parallel.

Smith Smart modeling means Smith Chart analysis results. Nonlinear StatEye give you statistical analysis visualization, much faster than using transient analysis.

Conclusion

Hearing from three engineers about how they use HSPICE in modeling and circuit simulation was rewarding, and I hope to make the event live next year. The SPICE marketplace has lots of competitors, so you have many choices. I still haven’t figured out how HSPICE and FineSIM product roadmaps converge or diverge. View the full video here.

Comments

0 Replies to “Modeling TSV, IBIS-AMI and SERDES with HSPICE”

You must register or log in to view/post comments.