A growing trend in system design is the use of multiple ICs mounted in advanced packages, especially in high-performance computing and AI. These modern packages now integrate multiple ICs, often with high-bandwidth memory (HBM), resulting in hundreds of thousands of connections that need proper verification. Traditional methods, often relying on manual processes and spreadsheets, simply cannot keep pace with this complexity. This blog post will explore how a new approach using formal verification is transforming the way IC package connectivity is verified, drawing insights from a recent white paper by Siemens EDA detailing the Innovator3D IC tool flow.

The Challenges of Modern IC Package Design

Historically, IC package design was relatively simple, mainly involving fanning out die bumps to connect to a printed circuit board. However, with heterogeneous integration and advanced packaging technologies, the task has become a complex system integration challenge. Substrate designers now juggle multiple inputs, often from multiple engineers developing their components simultaneously, and must ensure both electrical and functional correctness. The sheer number of connections, often exceeding 500,000, makes manual verification impractical, and relying on spreadsheets becomes error prone and tedious. The maximum number of rows in Excel is 1,048,576 which is not enough for many designs.

Limitations of Traditional Verification Methods

Traditional verification methods are struggling to keep up. Functional verification, which simulates the design to ensure it operates correctly, is challenging for package designs. It requires functional models for each die, models for discrete components, and testbenches. When chiplets, such as HBM, are involved, these models may not be readily available, and even if they are, package designers often lack the expertise to adapt and use them.

Layout versus schematic (LVS) verification, while helpful in ensuring the physical implementation matches the source netlist, does not verify the functional correctness of the design. It can catch shorts and opens, but it cannot confirm that the design works as intended. If the source netlist itself has errors, LVS will not catch them, giving a false sense of security.

Formal Verification: A New Paradigm

Formal verification provides an alternative solution by using mathematical analysis to exhaustively verify all interconnections between IC blocks. This method only requires two key pieces of information:

- The system top module with connectivity information

- Module port definitions of the dies

Formal verification does not require lengthy testbenches or assertions. It can detect connection errors, ensure the correctness of connections, and identify potential short circuits. Since the method uses mathematical analysis considering all possible stimulus, it can prove connections are correct without any overlooked scenarios.

Innovator3D IC and Check Connect

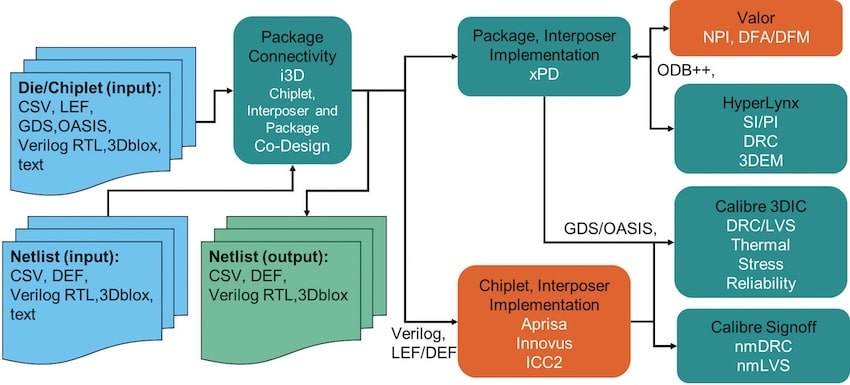

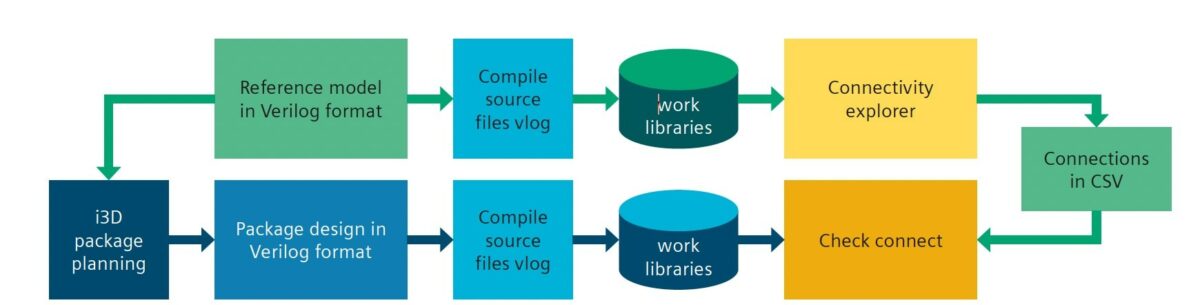

Siemens EDA’s Innovator3D IC (i3D) tool helps engineers tackle the complexities of modern package design. i3D collects data from various sources, such as die, BGA, and netlist data, and allows the creation of system connectivity. The connectivity can be exported in multiple formats, including Verilog, for verification purposes.

Siemens’ Check Connect is a formal verification tool that is used to verify the connectivity of a package design. It uses a golden reference model, often developed by the design team through the design phase and extensive simulation and automatically extracts the connections to verify the design. The tool works with the i3D package design tool to generate Verilog netlists and then verifies the connections. The tool can generate a missing-port report that lists the ports not covered by any connections, helping to identify potential issues in the reference model or the connection specifications. The tool is also very fast and can work on big systems because the design modules are treated as black boxes, focusing only on connections between blocks.

Benefits of the Formal Approach

- Exhaustive Verification: Formal methods mathematically analyze all possible scenarios, guaranteeing that connections are correct.

- Early Detection: Errors can be detected early, right after package prototyping, saving time and money.

- Automation: The entire flow is automatic, from creating connectivity specifications to verifying packaging output connectivity. The script is simple and can be reused for different projects.

- Speed: Automatic parallel algorithms on the compute grid can verify huge numbers of connections in minutes or even seconds. Test cases have shown verification times as low as 30 seconds for designs with over 20,000 connections and 56 seconds for designs with over 40,000 connections.

- Improved Reliability: Formal verification is critical in industries with strict regulatory standards, such as aerospace and automotive, because it can provide an exhaustive analysis of connections, and some tools are ISO 26262 certified.

Conclusion

The white paper demonstrates that formal verification is an effective approach for the challenges of modern IC package design. By automating the verification process, it ensures the correctness of connections early in the process, leading to improved quality and reduced time to market. The learning curve for setting up these formal tools takes only minutes. This approach is poised to become an essential part of the modern IC package design flow.

Read the 13 page white paper online showing how Innovator3D IC uses formal verification.

Related Blogs

- Electrical Rule Checking in PCB Tools

- Next Generation of Systems Design at Siemens

- Siemens Provides a Complete 3D IC Solution with Innovator3D IC

- 3DIC Verification Methodologies for Advanced Semiconductor ICs