At the November 14 Cadence Automotive Summit, Ian Dennison, Senior Group Director, outlined sensor enablement technologies and SoC mixed-signal design solutions, from Virtuoso electrically aware design with high current, high reliability, yield and performance tools and methodologies enabling ADAS/AV sensors for vehicle perception.

An ADAS/AV camera system was described as containing on the transmit side a Cadence Ethernet MAC, a BroadR-Reach PHY, filters, cables, and connectors to a decision-making board on the receiving side and accompanying simulation-based EMI verification, modeling, PCB power integrity analysis, S-parameter models to ensure data coming in is successfully received without resending.

The actual IP containing the automotive Ethernet MAC IP is available in 10Mbps Ethernet that replaces CAN, Flexray, 100Mbps which still demands image compression, and a higher than 1Gbps rate that avoids the need for image compression for the highest image quality and best object classification, along with DMA, APB configuration interface registers and a time stamp unit for Time Sensitive Networking to ensure camera data is not delayed. The automotive Ethernet MAC has received ASIL-B ready certification under the Automotive ISO 26262 standard.

ASIL compliance requires a quality management process and certification, a safety manual for SEooC, safety features description, failure mode effect, diagnostic analysis, and automotive safety kits for tools and flows. In implementing a system using Innovus, a time stamp unit (TSU), the TSU block is duplicated with timer outputs compared on a cycle-by-cycle basis to detect any faults as one of the safety mechanisms. Other considerations exist like creating safety boundaries where internal nets are maintained inside each TSU and interfaces nets are not routed over to avoid common mode failures in the duplicated TSUs.

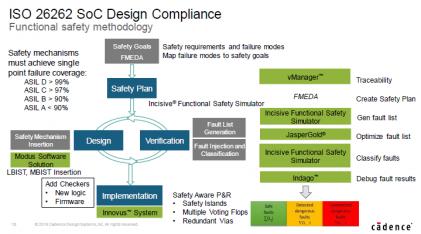

ISO 26262 SoC design compliance is ensured with the functional safety methodology described in the diagram. Some requirements for proper classification include continuous checks that are needed on the image sensor to enable failure signals to be raised within two frames. On-chip checkers are placed inside the chip to identify analog or digital functional failures that can result in image sensor row, column, ADC and clock failures. There are some types of image sensor failures that rely on DSP processes downstream to be properly detected.

There are some CIS ADAS/AV considerations that determine object classification success driven primarily by moving vehicle image quality. CIS ADAS/AV issues include high dynamic range (HDR) needed for bright/dark conditions, vehicle motion-induced rolling shutter distortion, LED street/vehicle lighting rolling shutter flicker mitigation needs, real-time shutter compensation, noise vulnerability, moving vehicle stabilization and gyroscope fusion and finally cost in a price sensitive automotive market.

A complete simulation platform for CIS analysis uses the ADE Product Suite and the Spectre family of simulators.

Designing needed CIS ADC high dynamic range includes considering the CIS fps/shutter speed that sets the ADC conversion rate, and CIS dynamic range sets the ADC resolution (60 dB and a range of 1000:1 means a 10-bit ADC). The Cadence methodology characterizes the ADCs in the presence of temporal noise.

Uniformity of the CIS arrays for proper design-in of electrical and electrical reliability is essential. Cadence Virtuoso electrically-aware design offers on-screen real-time parasitics and resistance analysis with colormaps and voltage drop summaries, and electromigration current flow, so they can be considered in the analysis and design.

Lidar uses several technologies such as CMOS used in SoCs for controller and Ethernet and image sensors, MEMS for scanning mirror, silicon photonics, III-V material for laser source, and system-in-package. The drive is towards low-cost, small form-factor lidar for automotive, medical, and industrial applications.

The end of Moore’s law is enabling a disaggregated SoC where packaging is the glue between different die where thermal integrity, AC coupling, losses, reflections, crosstalk, warping mitigation, thermal and electromagnetic integrity need to be comprehended and dealt with.

Silicon photonics for frequency modulated continuous wave (FMCW) requires 10 cm automotive lidar depth precision addressed with tighter control of laser modulation and an electro-optical phase-locked loop (PLL). A MEMs tunable laser producing a laser source is split down into two waveguides. One waveguide is sent to the target and the return signal is blended, using an FMCW with a frequency changing all the time and with the signature generating a beat frequency.

Silicon photonics and MEMS co-design are enabled with Spectre APS and AMS Designer, Virtuoso ADE, schematic and layout suites, along with tools from partners like Lumerical and Coventor.

Cadence’s Legato Reliability Solution has a design-for-reliability approach extending the lifetime of the chips. When a failure occurs, functional safety kicks in to stop a car, but tools are needed to help a design-for-reliability mindset where analog defect analysis occurs to reduce the test cost and eliminate test escapes, electro-thermal analysis prevents thermal overstress avoiding premature failures, and advanced aging analysis accurately predicts product wear-out.

In ADAS radar sensor design, antenna sizes are shrinking allowing on-chip integration. A 122GHz radar includes a low-noise amplifier (LNA), power amplifier, mixer, and two on-chip antennas.

The Virtuoso RF Solution allows multi-fabric RF in PCB, SiP and SoC and interfaces with Spectre RF, Allegro Sigrity and National Instruments’ Axiem. An ADAS radar transceiver design was illustrated showing stretchable transmission lines with pCells, matched RX & TX antennas, Spectre RF and Virtuoso ADE Assembler showing the noise figure, input matching, gain, and stability.

Virtuoso RF allows a layered extraction of modules with EM solvers using QRC (a parasitic extractor), Sigrity PowerSI (a 3D-EM solver), and NI’s Axiem (a 2.5D solver for planar elements). The Sigrity PowerSI 3D-EM has an RF-module package extraction and critical path S-parameter model extraction for layered structure designs (on-chip, package, and PCB).

Datacenters are well suited for labeling training datasets with a training engine run only once per dataset versus an inference engine that is run on every image from various sensors onboard the vehicle that feeds new data to the datacenter.

The labeling of the datasets generates a set of coefficients with various weights pushed to the car, which then does a single pass evaluation on the image and generates the most probable label for proper decision making.

System and software design follow a spectrum starting from workstation simulation with no specialized hardware, to Xcelium parallel simulation with hardware running at about 1KHz for software execution, moving to Palladium Z1 emulation with hardware running at ~1MHz for software execution, then to Protium S1 FPGA prototyping at ~10 MHz and finally with first silicon on a prototype board. This allows development of OS, middleware, firmware, and drivers in parallel with hardware-based simulation accelerating the functional verification. Early start to software development or the new hardware accelerate time-to-market.

The Cadence design enablement allows system and DSP design, advanced node SoC development, MEMS and Silicon photonics implementation, SiP integration and CNN software development, all in one interoperable environment that greatly enhances sensor design and opens design fabrics and opportunities leveraging improved accuracy, decision making, and reliability.

Read more here: Automotive Summit 2018 Proceedings

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.