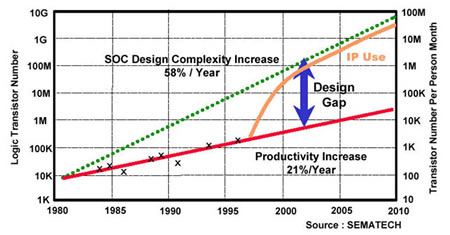

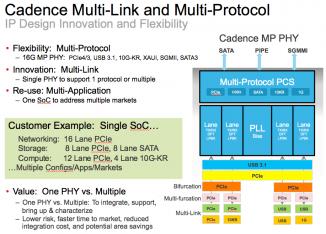

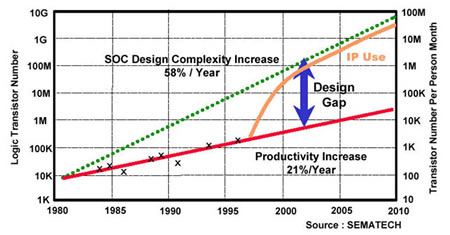

This white paper about Cadence innovative mixed-signal IP concept “Cadence Multi-Link PHY IP (SerDes, Analog Front-end, and DDR) to Design SoC Platform breaking the “Business Gap” on 14/16FF” describe the problem, the emergence of a “business gap” linked with incredibly high development cost when targeting most advanced FinFET technology nodes, and the solution, integrating a Multi-Link PHY IP. Chip makers targeting the lucrative market segments like FPGA, Mobile, Networking or Data Center are forced to jump on the most advanced technology node for several reasons. They all have to be the first to bring the highest possible processor performance or bandwidth (servers, networking), or the first to launch an Application Processor (smartphone) offering both maximum possible features, higher performance and at par or lower power consumption than the previous generation. The SoC development schedule is constrained by the market expectation, pushing for the lowest possible Time-To-Market (TTM). Designing a SoC on 14/16FF nm and below, also means finding a solution to a critical business problem linked with the increasingly high development cost. The IP reuse concept is born in the 1990’s to help optimizing the chip design. Commercial IP market took off in the 2000’s to solve the so-called “design gap”, as designer productivity didn’t grow fast enough to allow building System-on-Chip although CMOS technology scaling made it possible. In this white paper, the author introduces the “business gap” concept: amortizing the incredibly high development cost for a SoC targeting a single application is becoming extremely difficult if not impossible, except for very few applications like smartphone…  Taking 14/16nm FF node as an example, the average number of IP blocks in a SoC is about 120 (source: IBS report, 2014). Still in the same SoC, interfaces represent about 50 IP blocks. This Cadence Multi-link PHY IP concept applies to high speed SerDes based interfaces. Let’s make it clear: Multi-Link is much more than Multi-protocol, a 10 year old, very cleaver concept reaching the limit, due to the business gap. The figure below is very helpful to understand that the Multi-link concept provides the flexibility of Multi-protocol plus re-use capability (here is the innovation): a single SoC can be designed to address multiple markets or applications.

Taking 14/16nm FF node as an example, the average number of IP blocks in a SoC is about 120 (source: IBS report, 2014). Still in the same SoC, interfaces represent about 50 IP blocks. This Cadence Multi-link PHY IP concept applies to high speed SerDes based interfaces. Let’s make it clear: Multi-Link is much more than Multi-protocol, a 10 year old, very cleaver concept reaching the limit, due to the business gap. The figure below is very helpful to understand that the Multi-link concept provides the flexibility of Multi-protocol plus re-use capability (here is the innovation): a single SoC can be designed to address multiple markets or applications.  Let’s take a customer example as a real case. Designing a single but configurable SoC, this company has integrated 16 lanes Multi-Link PHY IP. To target Networking application, the PHY is configured as 16 lanes PCIe, to target Storage as 8 lanes PCIe, 8 lanes SATA and for Computing as a 12 lanes PCIe, 4 lanes 10G-KR. Amortizing the SoC development cost will be much easier as the ROI is now coming from three different markets, instead of a single application as it was the case before using the Multi-link concept. The benefits of using this Multi-link PHY IP concept are multiples as the various cost and resource intensive activities like IP integration, characterization setup and board design, qualification or PDK update are done only one time, leading to faster SoC design. Shorter TTM can be a priceless advantage for SoC addressing highly competitive markets. Such a Multi-protocols/Multi-links PHY IP offering Cost of Ownership (CoO) and TTM benefits all along the supply chain from fabless to foundries and EDA ecosystem. Cadence has enlarged this Multi-link concept to Analog Front End (AFE) IP for wireless communication, as well as to DDRn (LPDDRn) Memory Controller PHY IP. Reading this white paper, you will find much more detailed explanations which can’t fit in a blog like this, I really encourage you to read it (I must recognize that I’m the author…). You can access the white paper here. Moore’s law evolution is generating a “business gap”, designing a SoC on advanced technology nodes requires such high investment that the return may not be guaranteed if you target only one application. A conservative approach would be to keep designing on affordable nodes, 28nm or above, but it would prevent to benefit from extra performance and lower power, known to be the keys of success. Moving from chip architecture, one SoC targeting one application, to system architecture and creating a SoC platform allowing targeting several applications with the same SoC may break this “business gap”. This new approach is made possible by the flexibility offered by Multi-link PHY IP (SerDes or AFE). By Eric Esteve from IPNEST

Let’s take a customer example as a real case. Designing a single but configurable SoC, this company has integrated 16 lanes Multi-Link PHY IP. To target Networking application, the PHY is configured as 16 lanes PCIe, to target Storage as 8 lanes PCIe, 8 lanes SATA and for Computing as a 12 lanes PCIe, 4 lanes 10G-KR. Amortizing the SoC development cost will be much easier as the ROI is now coming from three different markets, instead of a single application as it was the case before using the Multi-link concept. The benefits of using this Multi-link PHY IP concept are multiples as the various cost and resource intensive activities like IP integration, characterization setup and board design, qualification or PDK update are done only one time, leading to faster SoC design. Shorter TTM can be a priceless advantage for SoC addressing highly competitive markets. Such a Multi-protocols/Multi-links PHY IP offering Cost of Ownership (CoO) and TTM benefits all along the supply chain from fabless to foundries and EDA ecosystem. Cadence has enlarged this Multi-link concept to Analog Front End (AFE) IP for wireless communication, as well as to DDRn (LPDDRn) Memory Controller PHY IP. Reading this white paper, you will find much more detailed explanations which can’t fit in a blog like this, I really encourage you to read it (I must recognize that I’m the author…). You can access the white paper here. Moore’s law evolution is generating a “business gap”, designing a SoC on advanced technology nodes requires such high investment that the return may not be guaranteed if you target only one application. A conservative approach would be to keep designing on affordable nodes, 28nm or above, but it would prevent to benefit from extra performance and lower power, known to be the keys of success. Moving from chip architecture, one SoC targeting one application, to system architecture and creating a SoC platform allowing targeting several applications with the same SoC may break this “business gap”. This new approach is made possible by the flexibility offered by Multi-link PHY IP (SerDes or AFE). By Eric Esteve from IPNEST

Instance

Array

(

[node_name] => Cadence

[node_id] => Array

(

[0] => 2

)

)

Instance

Array

(

[node_name] =>

[node_id] => Array

(

[0] => 2

)

[title] => Recent Forum Threads

)

Threads

XF\Mvc\Entity\ArrayCollection Object

(

[entities:protected] => Array

(

[24908] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 57

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24908

[node_id] => 2

[title] => CEO Andy Jassy’s 2025 Letter to Shareholders

[reply_count] => 14

[view_count] => 491

[user_id] => 36640

[username] => soAsian

[post_date] => 1775736884

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 99060

[first_post_reaction_score] => 1

[first_post_reactions] => {"1":1}

[last_post_date] => 1775789816

[last_post_id] => 99090

[last_post_user_id] => 38697

[last_post_username] => blueone

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 54

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 36640

[username] => soAsian

[username_date] => 0

[username_date_visible] => 0

[email] => jackmtsai@gmail.com

[custom_title] =>

[language_id] => 1

[style_id] => 0

[style_variation] =>

[timezone] => America/Chicago

[visible] => 1

[activity_visible] => 1

[user_group_id] => 2

[secondary_group_ids] =>

[display_style_group_id] => 2

[permission_combination_id] => 8

[message_count] => 419

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1608139716

[last_activity] => 1775769971

[last_summary_email_date] => 1719670845

[trophy_points] => 63

[alerts_unviewed] => 1

[alerts_unread] => 1

[avatar_date] => 0

[avatar_width] => 0

[avatar_height] => 0

[avatar_highdpi] => 0

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 0

[is_admin] => 0

[is_banned] => 0

[reaction_score] => 382

[warning_points] => 0

[is_staff] => 0

[secret_key] => 2oKeCTFkGUpMro5tcmj7WaY9HksB13Kw

[privacy_policy_accepted] => 1608139716

[terms_accepted] => 1608139716

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8515

[message_count] => 62326

[last_post_id] => 99090

[last_post_date] => 1775789816

[last_post_user_id] => 38697

[last_post_username] => blueone

[last_thread_id] => 24908

[last_thread_title] => CEO Andy Jassy’s 2025 Letter to Shareholders

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24892] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 61

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24892

[node_id] => 2

[title] => "Intel is proud to join the Terafab project with @SpaceX, @xAI, and @Tesla to help refactor silicon fab technology"

[reply_count] => 23

[view_count] => 3077

[user_id] => 90385

[username] => NY_Sam2

[post_date] => 1775574772

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 99001

[first_post_reaction_score] => 2

[first_post_reactions] => {"1":2}

[last_post_date] => 1775789065

[last_post_id] => 99089

[last_post_user_id] => 138698

[last_post_username] => bilau

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 58

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 90385

[username] => NY_Sam2

[username_date] => 0

[username_date_visible] => 0

[email] => petekennedy1989@gmail.com

[custom_title] =>

[language_id] => 1

[style_id] => 0

[style_variation] =>

[timezone] => America/New_York

[visible] => 1

[activity_visible] => 1

[user_group_id] => 2

[secondary_group_ids] =>

[display_style_group_id] => 2

[permission_combination_id] => 8

[message_count] => 40

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1642621712

[last_activity] => 1775739902

[last_summary_email_date] => 1767709207

[trophy_points] => 18

[alerts_unviewed] => 20

[alerts_unread] => 20

[avatar_date] => 0

[avatar_width] => 0

[avatar_height] => 0

[avatar_highdpi] => 0

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 0

[is_admin] => 0

[is_banned] => 0

[reaction_score] => 58

[warning_points] => 0

[is_staff] => 0

[secret_key] => egi-LmWHpsbQRZ7Y0Lk56hMyhUsrDhDE

[privacy_policy_accepted] => 1642621712

[terms_accepted] => 1642621712

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8515

[message_count] => 62326

[last_post_id] => 99090

[last_post_date] => 1775789816

[last_post_user_id] => 38697

[last_post_username] => blueone

[last_thread_id] => 24908

[last_thread_title] => CEO Andy Jassy’s 2025 Letter to Shareholders

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24912] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 65

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24912

[node_id] => 2

[title] => Big step for the 1.8 Tb/s ecosystem.

[reply_count] => 0

[view_count] => 57

[user_id] => 444140

[username] => moh.kolb

[post_date] => 1775776067

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 99080

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1775776067

[last_post_id] => 99080

[last_post_user_id] => 444140

[last_post_username] => moh.kolb

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 62

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 444140

[username] => moh.kolb

[username_date] => 0

[username_date_visible] => 0

[email] => moh@kolbehdari.com

[custom_title] =>

[language_id] => 1

[style_id] => 0

[style_variation] =>

[timezone] => America/Phoenix

[visible] => 1

[activity_visible] => 1

[user_group_id] => 2

[secondary_group_ids] =>

[display_style_group_id] => 2

[permission_combination_id] => 8

[message_count] => 11

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1775069311

[last_activity] => 1775776067

[last_summary_email_date] => 1775069311

[trophy_points] => 3

[alerts_unviewed] => 3

[alerts_unread] => 3

[avatar_date] => 0

[avatar_width] => 0

[avatar_height] => 0

[avatar_highdpi] => 0

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 0

[is_admin] => 0

[is_banned] => 0

[reaction_score] => 1

[warning_points] => 0

[is_staff] => 0

[secret_key] => EG539H6nqaiPLLZ4UXYEvAY-Py_6iJOA

[privacy_policy_accepted] => 1775069311

[terms_accepted] => 1775069311

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8515

[message_count] => 62326

[last_post_id] => 99090

[last_post_date] => 1775789816

[last_post_user_id] => 38697

[last_post_username] => blueone

[last_thread_id] => 24908

[last_thread_title] => CEO Andy Jassy’s 2025 Letter to Shareholders

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24910] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 69

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24910

[node_id] => 2

[title] => Why AI Chips Made In The U.S. Are Being Sent To Taiwan — Creating A Major Bottleneck

[reply_count] => 0

[view_count] => 144

[user_id] => 5

[username] => Daniel Nenni

[post_date] => 1775760897

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 99073

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1775760897

[last_post_id] => 99073

[last_post_user_id] => 5

[last_post_username] => Daniel Nenni

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 66

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 5

[username] => Daniel Nenni

[username_date] => 0

[username_date_visible] => 0

[email] => dnenni@semiwiki.com

[custom_title] => Founder

[language_id] => 1

[style_id] => 0

[style_variation] =>

[timezone] => America/Los_Angeles

[visible] => 1

[activity_visible] => 1

[user_group_id] => 3

[secondary_group_ids] => 4,5,132

[display_style_group_id] => 3

[permission_combination_id] => 88

[message_count] => 15469

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1280720820

[last_activity] => 1775778056

[last_summary_email_date] => 1605968657

[trophy_points] => 113

[alerts_unviewed] => 104

[alerts_unread] => 104

[avatar_date] => 1663211649

[avatar_width] => 110

[avatar_height] => 107

[avatar_highdpi] => 0

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 1

[is_admin] => 1

[is_banned] => 0

[reaction_score] => 9360

[warning_points] => 0

[is_staff] => 1

[secret_key] => 0HwyUVVHCwJotUUVEpvqAclfYJdGNPpw

[privacy_policy_accepted] => 0

[terms_accepted] => 0

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8515

[message_count] => 62326

[last_post_id] => 99090

[last_post_date] => 1775789816

[last_post_user_id] => 38697

[last_post_username] => blueone

[last_thread_id] => 24908

[last_thread_title] => CEO Andy Jassy’s 2025 Letter to Shareholders

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24909] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 73

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24909

[node_id] => 2

[title] => Intel-Sambanova AI Strategy

[reply_count] => 0

[view_count] => 166

[user_id] => 1305

[username] => KevinK

[post_date] => 1775751579

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 99068

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1775751579

[last_post_id] => 99068

[last_post_user_id] => 1305

[last_post_username] => KevinK

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 70

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 1305

[username] => KevinK

[username_date] => 0

[username_date_visible] => 0

[email] => kevin@kranen.com

[custom_title] =>

[language_id] => 1

[style_id] => 0

[style_variation] =>

[timezone] => America/Los_Angeles

[visible] => 1

[activity_visible] => 1

[user_group_id] => 2

[secondary_group_ids] =>

[display_style_group_id] => 2

[permission_combination_id] => 8

[message_count] => 750

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1307041560

[last_activity] => 1775777945

[last_summary_email_date] => 1657203603

[trophy_points] => 93

[alerts_unviewed] => 1

[alerts_unread] => 1

[avatar_date] => 0

[avatar_width] => 0

[avatar_height] => 0

[avatar_highdpi] => 0

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 0

[is_admin] => 0

[is_banned] => 0

[reaction_score] => 870

[warning_points] => 0

[is_staff] => 0

[secret_key] => d8MK99Btn0vCdz0LAv6U6Lcg678TyqUf

[privacy_policy_accepted] => 0

[terms_accepted] => 0

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8515

[message_count] => 62326

[last_post_id] => 99090

[last_post_date] => 1775789816

[last_post_user_id] => 38697

[last_post_username] => blueone

[last_thread_id] => 24908

[last_thread_title] => CEO Andy Jassy’s 2025 Letter to Shareholders

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24897] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 77

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24897

[node_id] => 2

[title] => UMC Reports Sales for March 2026

[reply_count] => 3

[view_count] => 291

[user_id] => 5

[username] => Daniel Nenni

[post_date] => 1775672344

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 99043

[first_post_reaction_score] => 1

[first_post_reactions] => {"1":1}

[last_post_date] => 1775749090

[last_post_id] => 99066

[last_post_user_id] => 138292

[last_post_username] => MKWVentures

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 66

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 5

[username] => Daniel Nenni

[username_date] => 0

[username_date_visible] => 0

[email] => dnenni@semiwiki.com

[custom_title] => Founder

[language_id] => 1

[style_id] => 0

[style_variation] =>

[timezone] => America/Los_Angeles

[visible] => 1

[activity_visible] => 1

[user_group_id] => 3

[secondary_group_ids] => 4,5,132

[display_style_group_id] => 3

[permission_combination_id] => 88

[message_count] => 15469

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1280720820

[last_activity] => 1775778056

[last_summary_email_date] => 1605968657

[trophy_points] => 113

[alerts_unviewed] => 104

[alerts_unread] => 104

[avatar_date] => 1663211649

[avatar_width] => 110

[avatar_height] => 107

[avatar_highdpi] => 0

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 1

[is_admin] => 1

[is_banned] => 0

[reaction_score] => 9360

[warning_points] => 0

[is_staff] => 1

[secret_key] => 0HwyUVVHCwJotUUVEpvqAclfYJdGNPpw

[privacy_policy_accepted] => 0

[terms_accepted] => 0

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8515

[message_count] => 62326

[last_post_id] => 99090

[last_post_date] => 1775789816

[last_post_user_id] => 38697

[last_post_username] => blueone

[last_thread_id] => 24908

[last_thread_title] => CEO Andy Jassy’s 2025 Letter to Shareholders

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24527] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 81

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24527

[node_id] => 2

[title] => Logic Contact from W to Mo, a press release by Applied Materials

[reply_count] => 3

[view_count] => 688

[user_id] => 90385

[username] => NY_Sam2

[post_date] => 1770775414

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 97371

[first_post_reaction_score] => 1

[first_post_reactions] => {"1":1}

[last_post_date] => 1775739902

[last_post_id] => 99061

[last_post_user_id] => 90385

[last_post_username] => NY_Sam2

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 58

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 90385

[username] => NY_Sam2

[username_date] => 0

[username_date_visible] => 0

[email] => petekennedy1989@gmail.com

[custom_title] =>

[language_id] => 1

[style_id] => 0

[style_variation] =>

[timezone] => America/New_York

[visible] => 1

[activity_visible] => 1

[user_group_id] => 2

[secondary_group_ids] =>

[display_style_group_id] => 2

[permission_combination_id] => 8

[message_count] => 40

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1642621712

[last_activity] => 1775739902

[last_summary_email_date] => 1767709207

[trophy_points] => 18

[alerts_unviewed] => 20

[alerts_unread] => 20

[avatar_date] => 0

[avatar_width] => 0

[avatar_height] => 0

[avatar_highdpi] => 0

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 0

[is_admin] => 0

[is_banned] => 0

[reaction_score] => 58

[warning_points] => 0

[is_staff] => 0

[secret_key] => egi-LmWHpsbQRZ7Y0Lk56hMyhUsrDhDE

[privacy_policy_accepted] => 1642621712

[terms_accepted] => 1642621712

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8515

[message_count] => 62326

[last_post_id] => 99090

[last_post_date] => 1775789816

[last_post_user_id] => 38697

[last_post_username] => blueone

[last_thread_id] => 24908

[last_thread_title] => CEO Andy Jassy’s 2025 Letter to Shareholders

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24906] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 85

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24906

[node_id] => 2

[title] => Why AI Chips Made In The U.S. Are Being Sent To Taiwan — Creating A Major Bottleneck

[reply_count] => 2

[view_count] => 322

[user_id] => 36640

[username] => soAsian

[post_date] => 1775689072

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 99054

[first_post_reaction_score] => 1

[first_post_reactions] => {"1":1}

[last_post_date] => 1775734737

[last_post_id] => 99058

[last_post_user_id] => 90182

[last_post_username] => siliconbruh999

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 54

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 36640

[username] => soAsian

[username_date] => 0

[username_date_visible] => 0

[email] => jackmtsai@gmail.com

[custom_title] =>

[language_id] => 1

[style_id] => 0

[style_variation] =>

[timezone] => America/Chicago

[visible] => 1

[activity_visible] => 1

[user_group_id] => 2

[secondary_group_ids] =>

[display_style_group_id] => 2

[permission_combination_id] => 8

[message_count] => 419

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1608139716

[last_activity] => 1775769971

[last_summary_email_date] => 1719670845

[trophy_points] => 63

[alerts_unviewed] => 1

[alerts_unread] => 1

[avatar_date] => 0

[avatar_width] => 0

[avatar_height] => 0

[avatar_highdpi] => 0

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 0

[is_admin] => 0

[is_banned] => 0

[reaction_score] => 382

[warning_points] => 0

[is_staff] => 0

[secret_key] => 2oKeCTFkGUpMro5tcmj7WaY9HksB13Kw

[privacy_policy_accepted] => 1608139716

[terms_accepted] => 1608139716

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8515

[message_count] => 62326

[last_post_id] => 99090

[last_post_date] => 1775789816

[last_post_user_id] => 38697

[last_post_username] => blueone

[last_thread_id] => 24908

[last_thread_title] => CEO Andy Jassy’s 2025 Letter to Shareholders

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24885] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 89

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24885

[node_id] => 2

[title] => Intel CEO embraces its 18A node for external customers as 18A-P gets 'inbound interest' — company cites increasing yields

[reply_count] => 13

[view_count] => 2147

[user_id] => 5185

[username] => Fred Chen

[post_date] => 1775354521

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 98939

[first_post_reaction_score] => 2

[first_post_reactions] => {"1":2}

[last_post_date] => 1775691112

[last_post_id] => 99055

[last_post_user_id] => 5185

[last_post_username] => Fred Chen

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 86

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 5185

[username] => Fred Chen

[username_date] => 0

[username_date_visible] => 0

[email] => chen.t.fred@gmail.com

[custom_title] =>

[language_id] => 1

[style_id] => 0

[style_variation] =>

[timezone] => America/Los_Angeles

[visible] => 1

[activity_visible] => 1

[user_group_id] => 4

[secondary_group_ids] =>

[display_style_group_id] => 4

[permission_combination_id] => 92

[message_count] => 2601

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1333032401

[last_activity] => 1775787090

[last_summary_email_date] => 1605940563

[trophy_points] => 113

[alerts_unviewed] => 0

[alerts_unread] => 0

[avatar_date] => 0

[avatar_width] => 0

[avatar_height] => 0

[avatar_highdpi] => 0

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 0

[is_admin] => 0

[is_banned] => 0

[reaction_score] => 1892

[warning_points] => 0

[is_staff] => 0

[secret_key] => 5m-bZq0HRSi9VA-96QONHJeevdQas5S8

[privacy_policy_accepted] => 0

[terms_accepted] => 0

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8515

[message_count] => 62326

[last_post_id] => 99090

[last_post_date] => 1775789816

[last_post_user_id] => 38697

[last_post_username] => blueone

[last_thread_id] => 24908

[last_thread_title] => CEO Andy Jassy’s 2025 Letter to Shareholders

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24898] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 93

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24898

[node_id] => 2

[title] => Intel Foundry Achieves Breakthrough with World's Thinnest GaN Chiplet Technology

[reply_count] => 0

[view_count] => 501

[user_id] => 5

[username] => Daniel Nenni

[post_date] => 1775674571

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 99044

[first_post_reaction_score] => 2

[first_post_reactions] => {"1":2}

[last_post_date] => 1775674571

[last_post_id] => 99044

[last_post_user_id] => 5

[last_post_username] => Daniel Nenni

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(

[User] => ThemeHouse\XLink\XF\Entity\User Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 66

[rootClass:protected] => XF\Entity\User

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[user_id] => 5

[username] => Daniel Nenni

[username_date] => 0

[username_date_visible] => 0

[email] => dnenni@semiwiki.com

[custom_title] => Founder

[language_id] => 1

[style_id] => 0

[style_variation] =>

[timezone] => America/Los_Angeles

[visible] => 1

[activity_visible] => 1

[user_group_id] => 3

[secondary_group_ids] => 4,5,132

[display_style_group_id] => 3

[permission_combination_id] => 88

[message_count] => 15469

[question_solution_count] => 0

[conversations_unread] => 0

[register_date] => 1280720820

[last_activity] => 1775778056

[last_summary_email_date] => 1605968657

[trophy_points] => 113

[alerts_unviewed] => 104

[alerts_unread] => 104

[avatar_date] => 1663211649

[avatar_width] => 110

[avatar_height] => 107

[avatar_highdpi] => 0

[avatar_optimized] => 0

[gravatar] =>

[user_state] => valid

[security_lock] =>

[is_moderator] => 1

[is_admin] => 1

[is_banned] => 0

[reaction_score] => 9360

[warning_points] => 0

[is_staff] => 1

[secret_key] => 0HwyUVVHCwJotUUVEpvqAclfYJdGNPpw

[privacy_policy_accepted] => 0

[terms_accepted] => 0

[vote_score] => 0

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[Forum] => XF\Entity\Forum Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 56

[rootClass:protected] => XF\Entity\Forum

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[discussion_count] => 8515

[message_count] => 62326

[last_post_id] => 99090

[last_post_date] => 1775789816

[last_post_user_id] => 38697

[last_post_username] => blueone

[last_thread_id] => 24908

[last_thread_title] => CEO Andy Jassy’s 2025 Letter to Shareholders

[last_thread_prefix_id] => 0

[moderate_threads] => 0

[moderate_replies] => 0

[allow_posting] => 1

[count_messages] => 1

[auto_feature] => 0

[find_new] => 1

[allow_index] => allow

[index_criteria] =>

[field_cache] => []

[prefix_cache] => []

[prompt_cache] => []

[default_prefix_id] => 0

[default_sort_order] => last_post_date

[default_sort_direction] => desc

[list_date_limit_days] => 0

[require_prefix] => 0

[allowed_watch_notifications] => all

[min_tags] => 0

[forum_type_id] => discussion

[type_config] => {"allowed_thread_types":["poll"]}

)

[_relations:protected] => Array

(

[Node] => XF\Entity\Node Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 55

[rootClass:protected] => XF\Entity\Node

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[node_id] => 2

[title] => SemiWiki Main Forum ( Ask the Experts! )

[description] => Post your questions to the experts here!

[node_name] =>

[node_type_id] => Forum

[parent_node_id] => 1

[display_order] => 1

[display_in_list] => 1

[lft] => 2

[rgt] => 3

[depth] => 1

[style_id] => 0

[effective_style_id] => 0

[breadcrumb_data] => {"1":{"node_id":1,"title":"Main Category","depth":0,"lft":1,"node_name":null,"node_type_id":"Category","display_in_list":true}}

[navigation_id] =>

[effective_navigation_id] =>

)

[_relations:protected] => Array

(

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

)

[_previousValues:protected] => Array

(

)

[_options:protected] => Array

(

)

[_deleted:protected] =>

[_readOnly:protected] =>

[_writePending:protected] =>

[_writeRunning:protected] =>

[_errors:protected] => Array

(

)

[_whenSaveable:protected] => Array

(

)

[_cascadeSave:protected] => Array

(

)

[_behaviors:protected] =>

)

[24896] => ThemeHouse\XPress\XF\Entity\Thread Object

(

[_uniqueEntityId:XF\Mvc\Entity\Entity:private] => 97

[rootClass:protected] => XF\Entity\Thread

[_useReplaceInto:protected] =>

[_newValues:protected] => Array

(

)

[_values:protected] => Array

(

[thread_id] => 24896

[node_id] => 2

[title] => Headline: Moving from Chaos to Control: The 1.8 Tb/s EM Corridor

[reply_count] => 1

[view_count] => 131

[user_id] => 444140

[username] => moh.kolb

[post_date] => 1775670224

[sticky] => 0

[discussion_state] => visible

[discussion_open] => 1

[discussion_type] => discussion

[first_post_id] => 99040

[first_post_reaction_score] => 0

[first_post_reactions] => []

[last_post_date] => 1775670349

[last_post_id] => 99041

[last_post_user_id] => 444140

[last_post_username] => moh.kolb

[prefix_id] => 0

[tags] => []

[custom_fields] => []

[vote_score] => 0

[vote_count] => 0

[featured] => 0

[type_data] => []

[index_state] => default

)

[_relations:protected] => Array

(