Network-on-Chip (NoC) is an emerging paradigm for communications within large VLSI systems implemented on a single silicon chip. Sgroi et al. call “the layered-stack approach to the design of the on-chip intercore communications the Network-on-Chip (NOC) methodology.” In a NoC system, modules such as processor cores, memories and specialized IP blocks exchange data using a network as a “public transportation” sub-system for the information traffic. A NoC is constructed from multiple point-to-point data links interconnected by switches (a.k.a. routers), such that messages can be relayed from any source module to any destination module over several links, by making routing decisions at the switches. A NoC is similar to a modern telecommunications network, using digital bit-packet switching over multiplexed links. Although packet-switching is sometimes claimed as necessity for a NoC, there are several NoC proposals utilizing circuit-switching techniques. This definition based on routers is usually interpreted so that a single shared bus, a single crossbar switch or a point-to-point network are not NoCs but practically all other topologies are. This is somewhat confusing since all above mentioned are networks (they enable communication between two or more devices) but they are not considered as network-on-chips. Note that some articles erroneously use NoC as a synonym for mesh topology although NoC paradigm does not dictate the topology. Likewise, the regularity of topology is sometimes considered as a requirement which is, obviously, not the case in research concentrating on “application-specific NoC topology synthesis”.

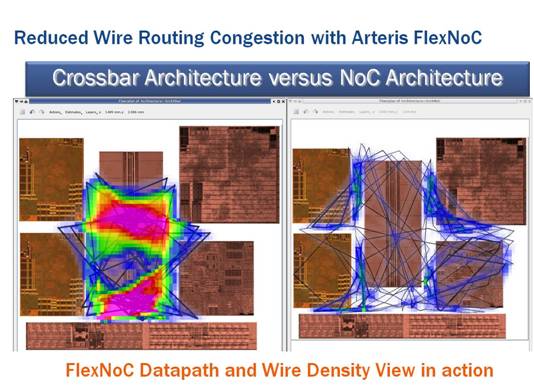

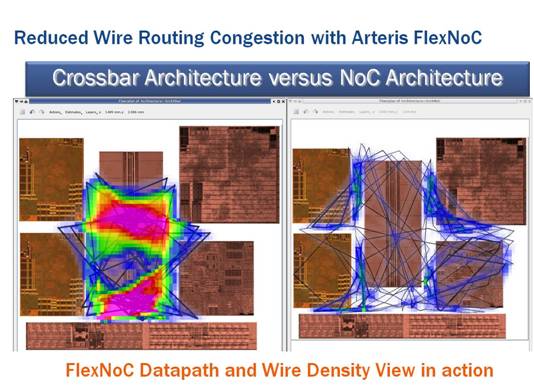

An interesting white paper from Arteris: “Routing Congestion: The Growing Cost of Wires in Systems-on-Chip” demonstrates how you can drastically reduce routing congestion by using a NoC. On this picture, you can see on the left part, the routing congestion areas, highlighted through a color code (purple= very strong congestion, red=strong congestion, yellow=medium, blue=no congestion), this will sounds familiar to anybody who has already used a floor planning tool. According with Jonah Probell: “…in the process of chip design, more can be done to improve P&R wire congestion by reducing the number of wires in the IP RTL before synthesis.”

For those like me who have used floor planning tools in the mid 90’s, to help customers to release to layout the RTL version of a chip with good chance to complete the lay out phase within a decent time period (say, a couple of weeks, as these chips were designed into a supercomputer, using the largest available BiCMOS base array, running at the highest possible internal frequency, which makes sense when you design a supercomputer…), it was common to spend weeks if not MONTHS to optimize the floor plan of the IC. I realize now that having the opportunity to use a NoC at that time would certainly help us to, either reduce the design cycle (thus the Time To Market for our customer, as well as the time spent by TI FAE team), either go higher in frequency, and help our customer to launch a more powerful product. I strongly encourage anybody involved (or interested) by on the edge SoC design techniques to download this paper from Arteris here.

Eric Esteve from IPNEST

Comments

0 Replies to “How to use NoC to avoid routing congestion”

You must register or log in to view/post comments.