Back in 2020 I first learned from Synopsys about how they had engineered a better way to do optimize layouts on digital designs by using machine learning techniques, instead of relying upon manual approaches. The product was named DSO.ai, standing for Design Space Optimization, and it produced a more optimal floor-plan in less… Read More

Tag: floor planning

How to use NoC to avoid routing congestion

Network-on-Chip (NoC) is an emerging paradigm for communications within large VLSI systems implemented on a single silicon chip. Sgroi et al. call “the layered-stack approach to the design of the on-chip intercore communications the Network-on-Chip (NOC) methodology.” In a NoC system, modules such as processor… Read More

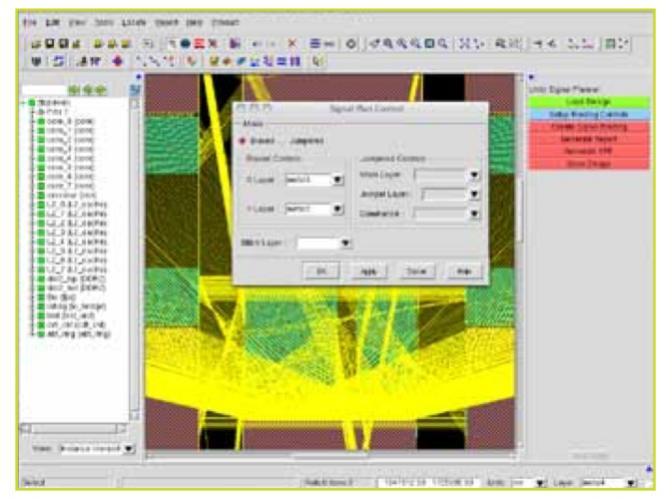

Custom Signal Planning Methodologies

It is no secret that custom ICs are getting larger and more complex and this has driven chip design teams to split up into smaller teams to handle the manual or semi-automated routing of the many blocks and hierarchical layers that go to make up such a design. These sub-teams don’t just need to handle the routing within their own block(s)… Read More