I read the semiconductor press, LinkedIn and social media (Twitter, Facebook) every morning along with an RSS feed that I setup, staying current on everything related to using EDA tools to make the task of SoC design a bit easier for design teams. A recent press release announced a tool called SoC Compiler, so my curiosity was piqued enough to read through it and then contact the EDA vendor to better understand what it was all about.

The company with SoC Compiler has been around now for 18 years, and is located in beautiful Grenoble, France. I’ve made one business trip to Grenoble visiting a customer and EDA vendor, and the mountain views are simply stunning, it was quite similar to seeing the Grand Tetons in Wyoming. Defacto Technologies is run by Chouki Aktouf, a PhD from Grenoble University, who founded the company in 2003. SoC Compiler is at version 9, because it’s the new product generation for what used to be called STAR, with a history of shipping for 15 years to front-end RTL designers.

What Does it Do?

In EDA there are lots of special interest groups that tend to create their own narrowly defined sub-flows and file formats, eventually gaining enough momentum to form a standard, so that multiple vendors can compete and cooperate in a bigger design flow. Here are some of the standards in use today for SoC design:

- Design Data, RTL or Gate-level

- IP block descriptions, IP-XACT

- Power Intent, UPF

- Physical cells, LEF/DEF

- Timing constraints, SDC

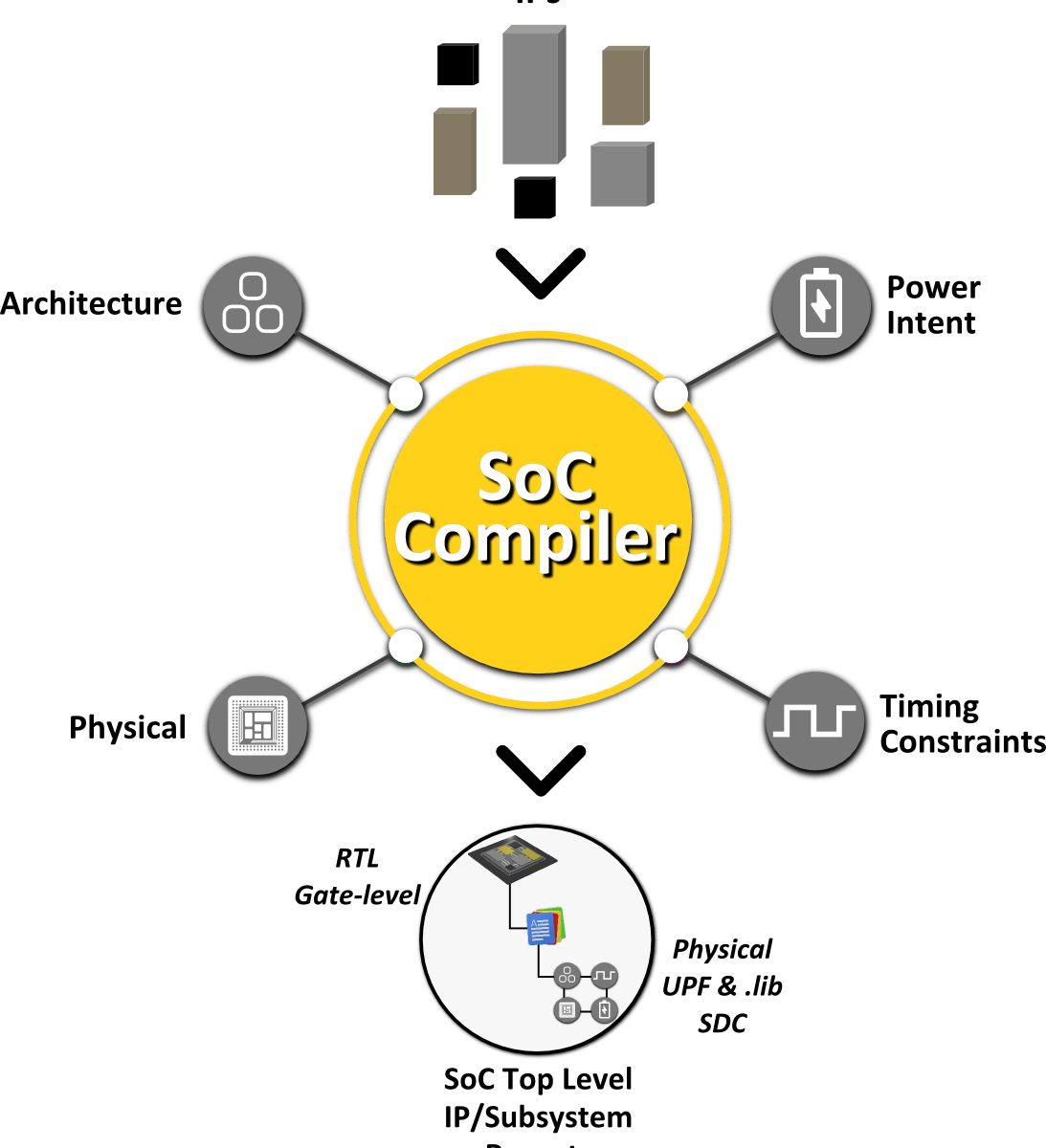

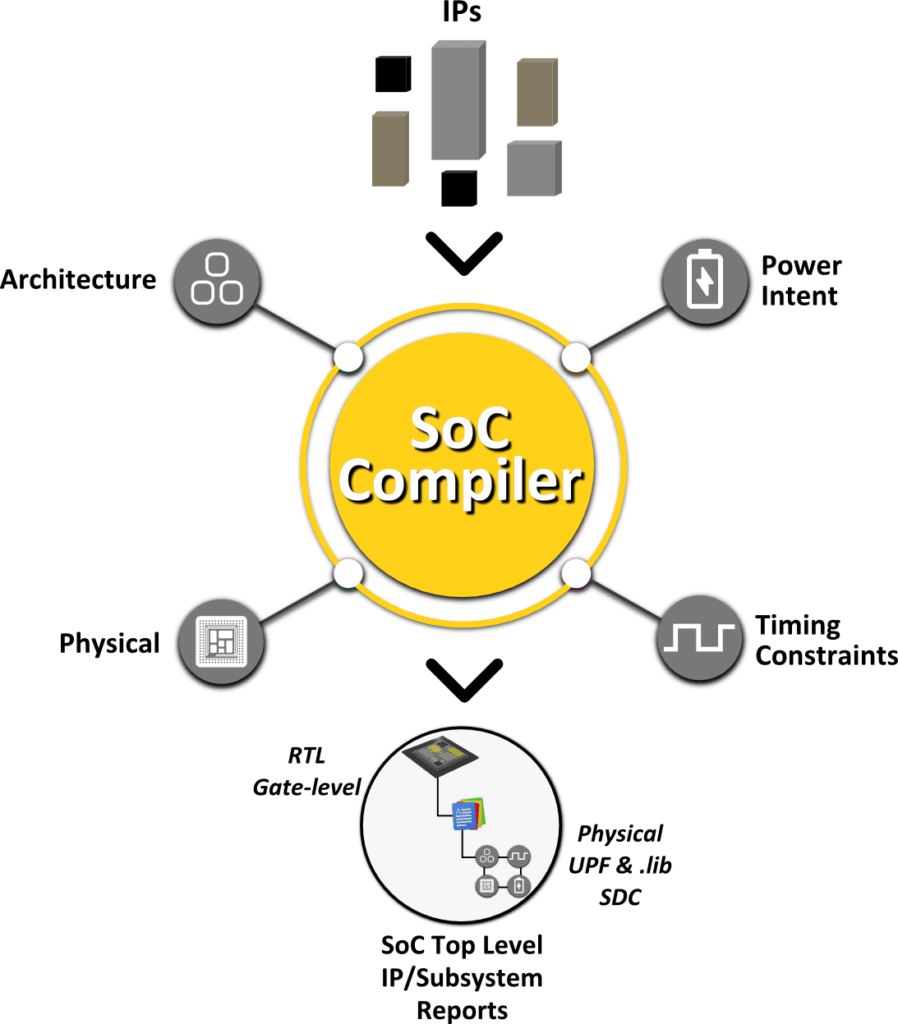

In the SoC Compiler tool it accepts as input all of these formats, then enables an engineer to efficiently and quickly assemble and create a new SoC, getting the RTL and design collateral ready for logic synthesis. Here’s the Defacto tool flow:

Modern SoCs can have hundreds of IP blocks, and when those blocks use the IP-XACT standard they can be read into SoC Compiler to check for correctness and a hierarchy can be quickly built for a new design. Defacto is a member of Accellera, and their tool works with the IP-XACT 2009 and 2014 standards. You can even write scripts to control how your IP blocks should be connected together, saving time from making manual file edits.

RTL design editing is made easier by the use of scripts or API languages like Tcl and Python, and SoC Compiler understands that when the RTL design is changed that the SDC and UPF collateral files also need to be updated automatically. Error-prone manual editing of SDC and UPF files in coherency with RTL changes is a thing of the past when using SoC Compiler.

Based on physical information contained in LEF/DEF files, SoC Compiler assists in the SoC creation, by being physically aware in order to optimize connectivity insertion. This helps in reducing the width of routing channels which helps in reducing the chip area.

SoC Compiler also provides the capabilities to explore and understand the Power intent and clock trees. A large set of linting checks are part of the embedded parser to ensure correctness, proper syntax and semantics for UPF and SDC files in conjunction with RTL.

Happy Customers

Two happy customers were mentioned in the press release:

- OpenFive – Semiconductor IP for AI, Edge Computing HPC and Networking

- SiPearl – Microprocessors for the European Processor Initiative

EDA Tool Flows

Since the file formats that SoC Compiler uses are defined by the semiconductor industry, design engineering teams can use this tool with any other EDA vendor tools, like: Synopsys, Cadence, Siemens, etc.

Summary

Defacto has shown that the SoC Compiler tool can be used in a fully automated design assembly flow, with IP insertion, IP stitching and design refactoring while creating top-level views. An internal CAD group could work for years to replicate all of the automation found within SoC Compiler, or they could instead consider an evaluation to witness how a proven tool benefits their SoC design team. Why develop something in-house, when there’s already a commercial product with a good track record?

Related Blogs

- CEO Interview: Dr. Chouki Aktouf of Defacto

- Power in Test at RTL Defacto Shows the Way

- Atos Crafts NoC, Pad Ring, More Using Defacto

- Build Custom SoC Assembly Platforms

- Another Application of Automated RTL Editing

- Analysis and Signoff for Restructuring

Comments

There are no comments yet.

You must register or log in to view/post comments.