Still thinking of Sonics as just a network-on-chip company? They are pivoting to become an SoC realization company, and in their seminar at #53DAC in Austin we saw an entirely new plan focused on heisting an extremely valuable commodity everyone else is missing.… Read More

iDRM – A Complete Design Rule Development System

Design rules are at the heart of the interface between the foundry and semiconductor designers, which makes them so critical. Traditionally, design rules and DRC decks have been developed manually with no or little automation. Design rule definitions are written using WORD or other general purpose office tools, and DRC decks… Read More

DRC Concept for IP Qualification and SoC Integration

In the history of semiconductor design and manufacturing, the age-old concept of DRC rule-deck qualification for handshake between design and manufacturing still applies strongly to produce working silicon. In fact, DRC clean GDSII works as the de facto golden gate between a design and a foundry for manufacturing the chip for… Read More

Moving chips from industrial to industrial IoT

IHS has put out its 1Q2016 Application Market Forecast predicting the highest growth rate segments for semiconductors over the next five years – and what was once old is new yet again. There it is, in the top right corner: industrial, projected to outpace even the automotive sector.… Read More

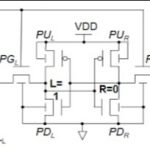

SRAM Optimization for 14nm and 28nm FDSOI

I’ve done SRAM and DRAM design before as a circuit designer from 1978-1986, but in 2016 there are so many more challenges to using 28nm and 14nm on FDSOI technology. One way to keep abreast of SRAM design is to read conference papers, so I just finished a paper from authors at STMicroelectronics and MunEDA presented at the IEEE… Read More

According with ST, SiC Power Devices will Accelerate Automotive Electrification

Silicon Carbide (SiC) is a very interesting material. If you find in nature the mineral moissanite, it will be only minute quantities in certain types of meteorite. The moissanite physical properties are very similar to these of diamond, in term of density and abrasive power. In the semiconductor industry, SiC is characterized… Read More

Sonics opens new strategy for SoC energy processing

Back in February when we shared the Sonics philosophy on the ICE-Grain Power Architecture for hardware-based SoC power management, I speculated we’d know more by DAC 2016. Sonics is hitting the road with a new live seminar coming to Silicon Valley this month and Austin during DAC – and the news is big.… Read More

How to Deal With Seven Design Closure Issues

The challenge of tracking design progress is a shared problem for individual designers, team leaders, and project managers. At each level the ability to step back from just reviewing error log files and seeing the arc of the whole design as it moves forward is valuable. The difficulty of seeing the whole picture is exacerbated when… Read More