FinFETs are fun! They certainly have kept me busy writing over the past year about the possibilities and probabilities of a disruptive technology that will dramatically change the semiconductor ecosystem. Now that 14nm silicon is making the rounds I will be able to start writing about the realities of FinFETs which is very exciting!… Read More

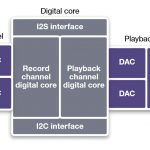

Shrinking audio creates issues and opportunities

There is a lot more to sound than meets the ear, and there a vast number of ways to deliver an audio experience. I recently trashed my gaming headset, replacing it with a Samson C03U mic and Audio-Technica ATH-PRO700MK2 headphones. It’s a huge upgrade, especially for podcasting, and I admit I was also motivated by research into digital… Read More

Modeling TSV, IBIS-AMI and SERDES with HSPICE

The HSPICE circuit simulator has been around for decades and is widely used by IC designers worldwide, so I watched the HSPICE SIG by video today and summarize what happened. Engineers from Micron, Altera and AMD presented on how they are using HSPICE to model TSVs, IBiS-AMI models and SERDES, respectively.… Read More

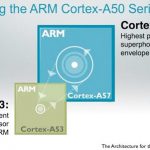

Developing ARM v8 Code…Today

You are going to be developing software for an SoC that contains an ARM Cortex-A57 64-bit CPU. Or perhaps it is an SoC containing ARM’s hybrid big.LITTLE multi-core architecture that combines one or more low power cores with some high power, high performance cores to get the best of both worlds: high throughput when it is needed… Read More

An Affordable AMS Tool Flow gets Integrated

EDA tools come in all sizes and price ranges, so I was pleased to readthat Tanner EDAhas completed an integration with Incentia. A few months ago Tanner announced their integration with Aldec for digital simulation, and today’s announcement extends their tool suite to include digital synthesis and static timing. Here’s… Read More

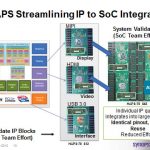

Help, my IP has fallen and can’t get up

We’ve been talking about the different technologies for FPGA-based SoC prototyping a lot here in SemiWiki. On the surface, the recent stories all start off pretty much the same: big box, Xilinx Virtex-7, wanna go fast and see more of what’s going on in the design. This is not another one of those stories. I recently sat down with Mick… Read More

Cadence, Synopsys, and Mentor on FinFETs

In my opinion, FinFETs will be the most significant piece of technology we, as semiconductor ecosystem people, will experience this decade. Seriously this is exciting stuff and one of the top search terms on SemiWiki for 6 months running. Here is a quick peek at what the top EDA companies will be talking about at the Common Platform… Read More

Verdi: No Requiem for Openness

I sat down last week for lunch with Michael Sanie. Mike and I go back a long way, working together at VLSI Technology (where his first job out of school was to take over the circuit extractor that I’d originally written) and then in strategic marketing at Cadence. Now Mike has marketing for (almost?) all of Synopsys’s … Read More

New PCI Express 3.0 Equalization Requirements

PCI Express 3.0 increased the supported data rate to 8 Gbps, which effectively doubles the data rate supported by PCI Express 2.0. While the data rate was increased, no improvement was made to the channels. As such, an 8 Gbps channel in PCIe 3.0 experiences significantly more loss than one implemented in PCIe 2.0. To compensate for… Read More

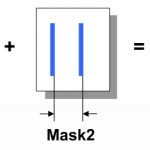

Double Patterning for IC Design, Extraction and Signoff

TSMC and Synopsys hosted a webinar in December on this topic of double patterning and how it impacts the IC extraction flow. The 20nm process node has IC layout geometries so closely spaced that the traditional optical-based lithography cannot be used, instead lower layers like Poly and Metal 1 require a new approach of using two… Read More