You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 14

[name] => Synopsys

[slug] => synopsys

[term_group] => 0

[term_taxonomy_id] => 14

[taxonomy] => category

[description] =>

[parent] => 157

[count] => 784

[filter] => raw

[cat_ID] => 14

[category_count] => 784

[category_description] =>

[cat_name] => Synopsys

[category_nicename] => synopsys

[category_parent] => 157

[is_post] =>

)

WP_Term Object

(

[term_id] => 14

[name] => Synopsys

[slug] => synopsys

[term_group] => 0

[term_taxonomy_id] => 14

[taxonomy] => category

[description] =>

[parent] => 157

[count] => 784

[filter] => raw

[cat_ID] => 14

[category_count] => 784

[category_description] =>

[cat_name] => Synopsys

[category_nicename] => synopsys

[category_parent] => 157

[is_post] =>

)

Donald Rumsfeld categorized what we knew into known unknowns and unknown unknowns. In a chip design, those unknown unknowns can bite you and leave you with a non-functional design, perhaps even intermittent failures which can be among the hardest problems to debug.

Chips are too big to do any sort of full gate-level simulation,… Read More

My very first thought when hearing about HSPICE is using it for IC simulation at the transistor-level, however it can also be used to simulate a package or PCB interconnect very accurately, like in the PCB layout of a DDR3 system where timing is critical. I attended a webinar this morning that was jointly presented by Zuken and Synopsys… Read More

FPGA design today involves not only millions of gates on the target device, but thousands of source files with RTL and constraints, often generated by multiple designers or third party IP providers. With modules organized in some logical way describing the design, designers brace themselves for synthesis and a possible avalanche… Read More

When I talk about social media and mention Synopsys you may quickly think of Karen Bartleson, the Senior Director of Community Marketing, because she:

…

Read More

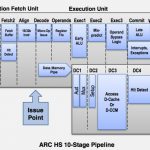

ARC is a family of configurable processors. Originally it was a standalone company in the UK (what is it with the UK and processor cores?) spun out from Argonaut Software. The A in ARC stood for Argonaut originally. ARC International was acquired by Virage and then Virage was acquired by Synopsys so now it is part of Synopsys Designware… Read More

Synopsys is taking IP-SOC 2013 seriously, as the company will hold several presentations, starting with a Keynote: “Virtual Prototyping – A Reality Check”, by Johannes Stahl, Director, Product Marketing, System-Level Solutions, Synopsys, highlighting current industry practice around putting virtual prototyping to work… Read More

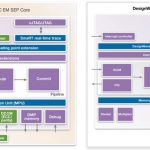

If you are familiar with Processor IP core, you certainly know DesignWare ARC EM4 core, 32-bit CPU that SoC designers can optimize for a wide range of uses, and differentiate by using patented configuration technology to tailor each ARC core instance to meet specific performance, power and area requirements. If you develop a product… Read More

In case you haven’t noticed, Synopsys has been in the press lately talking about their relationship with TSMC. Since I’m an internationally recognized industry expert they gave me a call for a briefing and I was happy to do it. Staying connected with the #1 EDA company is important and fun since I get to ask questions that most people… Read More

Harish Aepalais part of the Design Closure Methodology group at LSIand he recently talked about his ASIC handoff experience in a webinar. Harish works with logic and physical synthesis, timing constraints, RTL analysis and formal verification.

One challenge with ASIC handoff has been getting through design closure with the… Read More

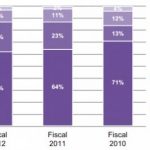

From chip IP vendor ARM Holdings to semiconductor foundry Taiwan Semiconductor, there have been many winners from the mobile device revolution that was sparked by Apple’s introduction of the iPhone. However, while these big-ticket names get all the fame and glory, the electronic design automation space (“EDA” for short) is … Read More