Ecosystem is everything when it comes to modern semiconductor design, especially if it is mobile. The fabless semiconductor industry has been all about ecosystem since the beginning and that is why we hold supercomputers in our hands today, believe it. After the invention of the transistor in 1947, and the invention of the integrated… Read More

A Brief History of TSMC OIP

The history of TSMC and its Open Innovation Platform (OIP) is, like almost everything in semiconductors, driven by the economics of semiconductor manufacturing. Of course ICs started 50 years ago at Fairchild (very close to where Google is headquartered today, these things go in circles). The planarization approach, whereby… Read More

Foundry 2.0: Why It Is Different And Why You Should Care

If you have been to an Ajit Manocha keynote recently, he talks a lot about Foundry 2.0. I covered his keynote at Semicon West in July here. Dan Hutcheson of VLSI Research interviewed Ajit about this new business model to identify it, see how it was different and see how GlobalFoundries were executing the model differently from the … Read More

Wall St. Takes the Wheel at Wintel

It now appears that Steve Ballmer was suddenly given his walking papers at the urging of an activist investor (ValueAct) and with the concurrence of Bill Gates. Wall Street’s growing impatience tends to coincide when the Innovators Dilemma scenario has taken hold of a company that has been unable to overcome its challengers. Why… Read More

Ballmer’s Retirement Leaves Nokia High and Dry

It looks to me as if Ballmer’s planned resignation from Microsoft is going to leave Nokia high and dry without an operating system. Because any successor to Ballmer will cancel Windows Phone which has managed to take Microsoft’s penetration in smartphones from 5% before it had a serious partnership with Nokia all … Read More

The TSMC OIP Technical Paper Abstracts are up!

The TSMC Open Innovation Platform® (OIP) Ecosystem Forum brings TSMC’s design ecosystem member companies together to share with our customers real-case solutions for customers’ design challenges and success stories of best practice in TSMC’s design ecosystem.

More than 90% of the attendees last year said “this… Read More

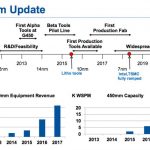

Intel Really is Delaying 14nm Move-in. 450mm is Slipping Too. EUV, who knows?

I attended the semi-annual SEMI Silicon Valley Lunch meeting last week. The semiconductor equipment people are the ones that really know what is going on. People can talk about capex numbers on conference calls but it is the equipment vendors who either do or do not get orders for particular types of equipment. In turn, the analysts… Read More

Microsoft Signals the Return of "Expensive Hardware, Cheap Software"

The announcement that Steve Ballmer will step down from Microsoft within the next 12 months and just weeks after kicking off a vast re-org focused on mobile devices can only mean that the future is coming much faster than Bill Gates or Steve Ballmer had ever expected and that without a radical adoption of hardware everywhere, it will… Read More

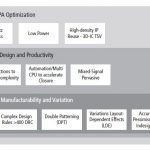

20nm IC production needs more than a ready Foundry

I think by now all of us know, or have heard about 20nm process node, its PPA (Power, Performance, Area) advantages and challenges (complexity of high design size and density, heterogeneity, variability, stress, lithography complexities, LDEs and so on). I’m not going to get into the details of these challenges, but will ponder… Read More

No Mention of 14nm at the 2013 Intel Developer Forum?

Yes, I will be going to IDF again this year, even though it is the same day as the Apple new product announcement. As a born again Apple Fan that is really saying something but Intel has done a great job of motivating the fabless semiconductor ecosystem and I thank them for that.

Unfortunately, noticeably missing from the IDF presentation… Read More

Solving the EDA tool fragmentation crisis