No need to explain the IoT acronym (Internet of Things) except that IoT doesn’t really describe a reality: do you really know about any “Thing” being directly connected to the Internet? In fact, there is probably some intermediate system linking this thing with the Cloud, like a smartphone, an Internet box, a PC, etc. Just take a … Read More

IP-SoC 2014 Top Class Presentations…

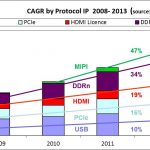

… were given to an ever shrinking audience. This is IP-SoC paradox: audience has enjoyed very good presentations made by Cadence, Synopsys or ST-Microelectronic, to name just a few. As far as I am concerned, I was happy to present the “Interface IP Winners and Losers (Protocols)” in the amphitheater during the first day, enjoying… Read More

What Presentations to Attend During IP-SoC 2014 ?

Will you go to Grenoble next week to attend to IP-SoC? I will do it and will certainly listen to these Keynote Talks:

- “Platform IP: the next wave for SOCs from IoT to Datacenter” by Tony King-Smith, Executive Vice President, Marketing , Imagination Technologies

- “From Server-class to IoT SoCs: Enabling System

Who Really Needs USB 3.1?

USB is certainly the most ubiquitous of the Interface protocols. I would bet that everybody is using USB everyday (I mean activate a USB connection, as we also use PCIe or SATA even if we don’t realize that we do it), but which application will get benefit of the 10 Gbps delivered by USB 3.1? Before precisely answering the question, … Read More

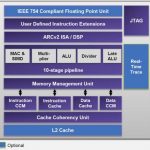

Linux and the ARC of the Coherent

Remember that thing called “real-time Linux”? Yeah, nobody else does either. As builds became configurable and clock speeds increased, embedded Linux manifested itself as fast enough for many applications – if a few other SoC details are addressed.

Most obvious for SoCs to run Linux is the need for a fully integrated MMU implementation.… Read More

Maker Movement Embraced by Major Semiconductor Companies

In 2005 with the development of the Arduino, everything changed for people building things that required a microcontroller. The Arduino brought with it a low price standard, and open, hardware platform and an easy to use open source development environment. It was … Read More

Design & EDA Collaboration Advances Mixed-Signal Verification through VCS AMS

Last week it was a rare opportunity for me to attend a webinar where an SoC design house, a leading IP provider and a leading EDA tool provider joined together to present on how the tool capabilities are being used for advanced mixed-signal simulation of large designs, faster with accuracy. It’s always been a struggle to combine design… Read More

Why do you need 9D Sensor Fusion to support 3D orientation?

Motion sensors are also commonly applied in a broad range of consumer products, including smartphones, wearable devices, game controllers and sports watches, with applications ranging from screen orientation to indoor navigation. If you desire to build an Inertial Measurement Unit (IMU) to efficiently compute 3D orientation,… Read More

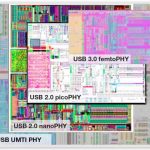

USB 3.0 IP on FinFET may stop port pinching

Sometimes a standard is a victim of its own success, at least for a while as the economics catch up to the technology. When a standard like USB 3.0 is announced, with a substantial performance increase over USB 2.0, some of the use cases come on board right away. Others, where vendors enjoy a decent ROI with good-enough performance,… Read More

How to Trim Automotive Sensor?

The electronic content in automotive is exploding, the market for automotive electronics systems is expected to grow from $170 billion in 2011 to $266 billion by 2016 (Strategy Analytics). When you seat in a brand new car, you immediately see the difference with a ten or even five years old vehicle, as you can exercise MP3 music readers,… Read More