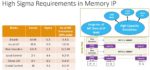

Looking at a typical SoC design today it’s likely to contain a massive amount of memory IP, like: RAM, ROM, register files. Keeping memory close to the CPU makes sense for the lowest latency and highest performance metrics, but what about process variations affecting the memory operation? At the recent DAC conference held… Read More

Semiconductor Intellectual Property

CEO Interview: Charlie Janac of Arteris IP

Charlie Janac is president and CEO of Arteris IP where he is responsible for growing and establishing a strong global presence for the company that is pioneering the concept of NoC technology. Charlie’s career spans over 20 years and multiple industries including electronic design automation, semiconductor capital equipment,… Read More

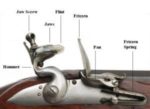

A Historical Case for Precision – or How a Gun Made in a Dungeon Changed the World

We take for granted today the staggering precision of modern technology. Cars, electronics, robots and medical equipment, all come off the factory floor composed of effortlessly interchangeable parts; but this was not always the case. In the late 18th century most things that required any kind of precision were made by hand, … Read More

PCI Express in Depth – Physical Layer

In the last article, I wrote about the PCIe basic concepts. This article will reach the physical layer of the PCIe standard.

The lowest PCI Express architectural layer is the Physical Layer. This layer is responsible for actually sending and receiving all the data to be sent across the PCI Express link. The Physical Layer interacts… Read More

PCI Express in Depth

This is another post that was requested by a user, and as always i’ll do my best to put in a few articles the basic information that you’ll need to understand how it works at depth level.

PCI Express (or PCIe) is a high-speed serial computer expansion bus designed to replace the older PCI, PCI-X and AGP standards.

The first… Read More

ARC Processor Virtual Summit!

The ARC Processor has a rich history. Originally named the Argonaut RISC Processor, it was designed for the Nintendo Game Systems in the 1990s. Argonaut Technologies Limited later became ARC International. My first intimate exposure to ARC was in 2009 when Virage Logic acquired ARC. A year later Virage was acquired by Synopsys… Read More

Major Hardware Security Initiative Adds Tortuga Logic

You can update ..Generally, I’m a fan of letting market forces figure out best solutions to whatever evolving needs we may have, but I’m enough of a realist to accept that’s not a workable answer to every need. Some problems need a top-down fix. However, we can’t expect policymakers or industry consortia to create compliance demands… Read More

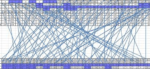

Interconnect Basics: Wires to Crossbar to NoC

To many of us, if we ever think about interconnect on an SoC, we may think delay, power consumption, congestion, that sort of thing. All important points from an implementation point of view, but what about the functional and system implications? In the early days, interconnect was very democratic, all wires more or less equal, … Read More

RISC-V SDKs, from IP Vendor or a Third Party?

Like many of us, I’m a fan of open-source solutions. They provide common platforms for common product evolution, avoiding a lot of unnecessary wheel re-invention, over and over again. Linux, TensorFlow, Apache projects, etc., etc. More recently the theme moved into hardware with OpenCores and now the RISC-V ISA. All good stuff.… Read More

CEO Interview: Ted Tewksbury of Eta Compute

Tell me about Eta Compute’s vision?

We envision a world where intelligent devices at the network edge make everyones’ lives safer, healthier, more comfortable, and convenient without sacrificing privacy and security.

How do you hope to achieve this?

We achieve this by providing the lowest power and most energy efficient machine… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era