RISC-V have great adoption and momentum. One of the key benefits of RISC-V is the ability for SoC designers to extend its instruction sets to accelerate specific algorithms. Andes’ ACE (Andes Custom Extensions) allow customers to quickly create, prototype, validate and ultimately implement custom memories, dedicated ports… Read More

Semiconductor Intellectual Property

#60DAC Update from Arteris

I met up with Andy Nightingale, VP Product Marketing and Michal Siwinski, Chief Marketing Officer of Arteris at #60DAC for an update on their system IP company dealing with SoCs and chiplet-based designs. SemiWiki has been blogging about Arteris since 2011, and the company has grown enough in those 12 years to have an IPO, see their… Read More

Next-Gen AI Engine for Intelligent Vision Applications

Artificial Intelligence (AI) has witnessed explosive growth in applications across various industries, ranging from autonomous vehicles and natural language processing to computer vision and robotics. The AI embedded semiconductor market is projected to reach $800 billion by year 2030. Compare this with just $48 billion… Read More

VC Formal Enabled QED Proofs on a RISC-V Core

The Synopsys VC Formal group have a real talent for finding industry speakers to talk on illuminating outside-the-box-topics in formal verification. Not too long ago I covered an Intel talk of this kind. A recent webinar highlighted use of formal methods used together with a cool technique I have covered elsewhere called Quick… Read More

Alphawave Semi Visit at #60DAC

On Wednesday at #60DAC I met Sudhir Mallya, Sr. VP Corporate Marketing at Alphawave Semi to get an update about what’s been happening at their IP company and with industry trends. The tagline for their company is: Accelerating the Connected World; and they have IP for connectivity, offer chiplet solutions, and even provide… Read More

Agile Analog Visit at #60DAC

Chris Morrison, Director of Product Marketing at Agile Analog met with me on the Tuesday at DAC this year, and I asked what has changed in the last year for their analog IP business. The short answer is that the company has initially built up foundation IP for Analog Mixed-Signal (AMS) uses, then recently added new IP for data conversion,… Read More

Upskill Your Smart Soldiers and Conquer the Chip War in Style!

My recent article, ‘Chip War without Soldiers’ explained the importance of upskilling and preparing the chip design workforce in this current scenario, and it also explained how it will lead to ‘Fabs without Chips’ if we don’t prioritize it. VLSI Engineers are the pillars of the semiconductor industry, and they can only transform… Read More

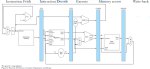

Back to Basics – Designing Out PPA Risk

I wrote earlier about managing service-level risk in SoC design, since the minimum service level a system can guarantee under realistic traffic is critical to OEM guarantees of dependable system performance. An ABS design which might get bogged down in traffic under only 0.1% of scenarios is of no use to anyone. That said, meeting… Read More

Mirabilis Invites System Architects at DAC 2023 in San Francisco

System architects have a difficult task of choosing the most efficient architecture by exploring alternative approaches, while tracking and testing requirements. Using a Model-Based Systems Engineering (MBSE) approach is recommended to achieve these goals, before getting mired in low-level implementation details like… Read More

CEO Interview: Ashraf Takla of Mixel

Ashraf Takla is Founder and CEO of Mixel Inc., which he founded in 1998 and is headquartered in San Jose, CA. Mixel is a leading provider of mixed-signal IPs and offers a wide portfolio of high-performance mixed-signal connectivity IP solutions. Mixel’s mixed-signal portfolio includes PHYs and SerDes, such as MIPI D-PHY, MIPI… Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry