The Network On Chip (NoC) concept is recent, about 10 years old, and the first implementation of commercially available NoC IP has happened in 2006. Should we drop the concept so quickly after it has been introduced? In fact, I don’t think so… But we could brain storm and imagine the new functions that could be implemented within or… Read More

Semiconductor Intellectual Property

ARM Cortex SoC Prototyping Platform for Industrial Applications

If your next SoC uses an ARM Cortex-A9 and has an industrial application, then you can save much design and debug time by using a prototyping platform. The price to prototype is quite affordable, and the methodology has a short learning curve. Bill Tomasan Aldec Research Engineer conducted a webinar today on: ARM Cortex SoC Prototyping… Read More

Will next generation Mobile Devices support PCI Express? M-PCIe is coming fast!

Those who have read the numerous articles I have written about MIPI, or PCIe, or the fusion of both named “Mobile Express” know my position: the question is not “Will Mobile devices support PCI Express?” but “When will we see Mobile devices integrating Mobile Express?” I was not really surprised by the Press Release that Cadence … Read More

Cadence To Acquire Tensilica

You have probably already seen the news: Cadence is acquiring Tensilica for $380M. Cadence has been relatively late to the IP party compared to Synopsys. In contrast, Mentor was early, got into the IP business before it was really profitable and ended up shutting down the business.

Tensilica is quite sizable. It has over 200 licensees,… Read More

Qualcomm and Intel Dynasty Scenario at 14nm

At a different time, but certainly within the past 12 months, Paul Otellini was asked if Intel would be a Foundry for Qualcomm. His reply was that it did not leave a good taste in his mouth. Nevertheless it was not rejected and the door that remained open just a crack is likely to swing open for Qualcomm, the premier mobile silicon supplier… Read More

Multiprotocol 10G-KR and PCIe Gen-3 PHY IP will support big data and smartphone explosion

We have frequently said in Semiwiki how crucial is it for the SC industry to benefit from high quality PHY IP… even if, from a pure business point of view (MBA minded), PHY IP business does not look so attractive. In fact, to be able to design on-the-edge SerDes and PLL (the two key pieces), you need to build and maintain a highly skilled… Read More

OTP based Analog Trimming and Calibration

Embedded NVM technology based functions can be implemented in large SoC designed in advanced technology nodes down to 28nm, as there is no requirement for extra mask levels, like when integrating Nand Flash, negatively impacting the final cost. And it is also possible to integrate One Time Programmable (OTP) to store trim and … Read More

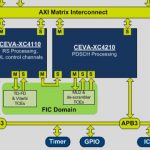

MUST: DSP ready solution for tomorrow smartphone based on CEVA-XC 4000

Like Guiness dark beer, competition is good for you! I mean good for end user, as it pushes DSP IP supplier to provide ever better solution. I am not talking about me-to type of competition, like that we have seen in the past with IBM trying to displace TI at Nokia, by offering a LEAD (DSP IP core from TI used in every NOKIA wireless phone… Read More

Modeling TSV, IBIS-AMI and SERDES with HSPICE

The HSPICE circuit simulator has been around for decades and is widely used by IC designers worldwide, so I watched the HSPICE SIG by video today and summarize what happened. Engineers from Micron, Altera and AMD presented on how they are using HSPICE to model TSVs, IBiS-AMI models and SERDES, respectively.… Read More

Innovative or Die, NoC IP Market is Cruel…

I have blogged in 2011 about the Arteris-Sonics case, initiated by Sonics, claiming that Arteris NoC IP product was infringing Sonics patent. In this article, we have seen that the architecture of Sonics interconnects IP product was not only older but also different from Arteris’ NoC architecture: the products launched initially… Read More

Is Intel About to Take Flight?