Flex Logix has been heads-down for the last several months working toward customer implementations of their EFLX reconfigurable RTL IP cores. Today, they’ve announced a family of 10 hard IP cores ready in TSMC 40ULP, and provided an update to their roadmap for us.… Read More

Score 1 for IDMs vs Fabless Intel King of the Photonics Hill in Data Centers

For those of you waiting with baited breath to see the Fabless community with the likes of Broadcom or Qualcomm challenge Intel in the data center space, you were just dealt a significant blow. Intel debuted their long awaited silicon photonics modules for what they called “lightning-fast” connectivity in data centers. Intel … Read More

Optimization and verification wins in IoT designs

Designers tend to put tons of energy into pre-silicon verification of SoCs, with millions of dollars on the line if a piece of silicon fails due to a design flaw. Are programmable logic designers, particularly those working with an SoC such as the Xilinx Zynq, flirting with danger by not putting enough effort into verification?… Read More

Webinar alert – Hybrid prototyping for ARMv8

All the talk about ARM server SoCs has been focused on who will come up with the breakthrough chip design. Watching trends like OPNFV develop suggests the big breakthrough is more likely to come on the ARMv8 software side. How do you quickly validate ARMv8 software when you don’t have the exact ARMv8 SoC target?… Read More

Time-saving modules expand Prototype Ready family

A big advantage of FPGA-based prototyping is the ability to run real-world I/O at-speed, significantly faster and more accurately than hardware emulation systems typically requiring a protocol adapter. Dealing with real-world I/O means more thorough verification of SoC integration, and the opportunity to optimize systems… Read More

Xilinx is Killing Altera!

At a recent outing with FPGA friends from days gone by, the long running Xilinx vs Altera debate has come to an end. The bottom line is that Xilinx has used the FUD (fear, uncertainty, and doubt) of the Intel acquisition quite effectively against Altera and is racking up 20nm and 16nm design wins at an alarming rate. It will be a while … Read More

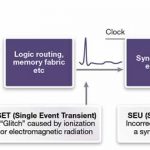

TMR approaches should vary by FPGA type

We’ve introduced the concepts behind triple modular redundancy (TMR) before, using built-in capability in Synopsys Synplify Premier to synthesize TMR circuitry into FPGAs automatically. A recent white paper authored by Angela Sutton revisits the subject… Read More

S2C tutorial and PROTOTYPICAL debut at DAC

It’s been a busy few days here in Canyon Lake, and we’re ready to share exciting news in advance of #53DAC coming up on Monday, June 6[SUP]th[/SUP]. S2C is offering a technical program tutorial on “Overcoming the Challenges of FPGA Prototyping” followed by the launch of our latest book project, “PROTOTYPICAL”, including a field… Read More

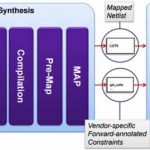

One FPGA synthesis flow for different IP types

Both Altera and Xilinx are innovative companies with robust ecosystems, right? It would be a terrible shame if you located the perfect FPGA IP block for a design, but couldn’t use it because it was in the “wrong” format for your preferred FPGA. What if there were a way around that?

There is a compelling argument to use each FPGA vendor’s… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior