SoC designs are getting more complex, resulting in a higher level of difficulty to get anything done. This trend is well-known. What I want to focus on here is how to deal with the issue of complexity. There are many approaches to taming this problem — faster algorithms for one, and improved algorithm efficiency or the ability to run… Read More

EDA Tool Support for GAA Process Designs

With the announcement of early PDK availability for the 3nm GAA process node, designers are extremely interested in the characteristics of the new “gate-all-around” transistor structure and how it compares to the existing FinFET device. The GAA transistor has been denoted as a (horizontal) nanowire or nanosheet.

I will talk… Read More

TSMC Sets the Stage for a Great 2021!

TSMC is the bellwether for not just the semiconductor industry but the worldwide economy. TSMC makes semiconductors, semiconductors are where electronics begin and electronics are the foundation of modern life, absolutely.

Apple is also a key economic indicator and as we all know Apple is a strategic partner of TSMC. The Apple… Read More

From Moore’s Law to Moortec’s Law!

No-one likes being put on the spot and yet we all like a forecast…and as we all know, the only guarantee with a forecast is that it is wrong. Sports commentators have carved out a special niche for themselves with the ‘commentators curse’, just as they extol the virtues of an individual or a team, the sporting gods prove them wrong in … Read More

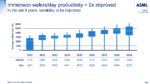

Imec Technology Forum and ASML

On Thursday July 9 Imec held a virtual technology forum. Imec is one of the premier research organizations working on semiconductor technology and their forums are always interesting. My area of interest is process technology and the following are my observation in that area from the forum.

Luc Van Den Hove

Luc Van Den Hove is the… Read More

Designing AI Accelerators with Innovative FinFET and FD-SOI Solutions

I had the pleasure of spending time with Hiren Majmudar in preparation for the upcoming AI Accelerators webinar. As far as webinars go this will be one of the better ones we have done. Hiren has deep experience in both semiconductors and EDA during his lengthy career at Intel and now with a pure play foundry. He is intelligent, personable,… Read More

How About a Faster Fast SPICE? Much Faster!

When Analog FastSPICE was first introduced in 2006 it changed the landscape for high performance SPICE simulation. During the last 14 years it has been used widely to verify advanced nanometer designs. Of course, since then the most advanced designs have progressed significantly, making verification even more difficult. Just… Read More

Staying on the Right Side in Worst Case Conditions – Performance (Part 2)

In this, the second part of a two-part series we delve further into defining worst case, this time focusing specifically on device performance.

In the last blog we talked about the steady increase in power density per unit silicon area and how worst case is definitely getting worse. We discussed how in each new FinFET node the dynamic… Read More

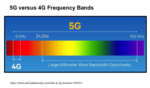

Contact over Active Gate Process Requirements for 5G

Summary

A recent process enhancement in advanced nodes is to support the fabrication of contacts directly on the active gate area of a device. At the recent VLSI 2020 Symposium, the critical advantages of this capability were highlighted, specifically in the context of the behavior of RF CMOS devices needed for 5G designs.

Introduction… Read More

Multi-Vt Device Offerings for Advanced Process Nodes

Summary

As a result of extensive focus on the development of workfunction metal (WFM) deposition, lithography, and removal, both FinFET and gate-all-around (GAA) devices will offer a wide range of Vt levels for advanced process nodes below 7nm.

Introduction

Cell library and IP designers rely on the availability of nFET and pFET… Read More

Intel, Musk, and the Tweet That Launched a 1000 Ships on a Becalmed Sea