Large language model (LLM) processing dominates many AI discussions today. The broad, rapid adoption of any application often brings an urgent need for scalability. GPU devotees are discovering that where one GPU may execute an LLM well, interconnecting many GPUs often doesn’t scale as hoped since latency starts piling up with… Read More

LIVE WEBINAR: Accelerating Compute-Bound Algorithms with Andes Custom Extensions (ACE) and Flex Logix Embedded FPGA Array

RISC-V have great adoption and momentum. One of the key benefits of RISC-V is the ability for SoC designers to extend its instruction sets to accelerate specific algorithms. Andes’ ACE (Andes Custom Extensions) allow customers to quickly create, prototype, validate and ultimately implement custom memories, dedicated ports… Read More

400 GbE SmartNIC IP sets up FPGA-based traffic management

Sustaining wire-speed 400 GbE transfers is only a first step in managing enterprise traffic. Adding rules-based filtering to sift packets in real time can stress most networking hardware to a breaking point, slowing down an entire network. Architects are trying to spread these loads, distributing intelligent traffic management… Read More

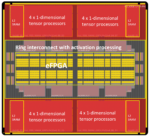

eFPGA Enabled Chiplets!

With our continuing chiplet coverage I found this of great interest. I have always felt that eFPGAs and chiplets are a natural fit for the next generation of chip design and this is an excellent example. As we design with chiplets one of the challenges is verification/validation in regards to performance and interoperability. … Read More

Reconfigurable DSP and AI IP arrives in next-gen InferX

DSP and AI are generally considered separate disciplines with different application solutions. In their early stages (before programmable processors), DSP implementations were discrete, built around a digital multiplier-accumulator (MAC). AI inference implementations also build on a MAC as their primitive. If the interconnect… Read More

The Rise of the Chiplet

The emergence of chiplets as a technology is an inflection point in the semiconductor industry. The potential benefits of adopting a chiplets-based approach to implementing electronic systems are not a debate. Chiplets, which are smaller, pre-manufactured components can be combined to create larger systems, offering benefits… Read More

eFPGA goes back to basics for low-power programmable logic

When you think “FPGA,” what comes to mind? Massive, expensive parts capable of holding a lot of logic but also consuming a lot of power. Reconfigurable platforms that can swallow RTL for an SoC design in pre-silicon testing. Big splashy corporate acquisitions where investors made tons of money. Exotic 3D packaging and advanced… Read More

Achronix on Platform Selection for AI at the Edge

Colin Alexander ( Director of product marketing at Achronix) released a webinar recently on this topic. At only 20 minutes the webinar is an easy watch and a useful update on data traffic and implementation options. Downloads are still dominated by video (over 50% for Facebook) which now depends heavily on caching at or close to … Read More

eFPGAs handling crypto-agility for SoCs with PQC

With NIST performing its down-select to four post-quantum cryptography (PQC) algorithms for standardization in July 2022, some uncertainty remains. Starting an SoC with fixed PQC IP right now may be nerve-wracking, with possible PQC algorithm changes before standardization and another round of competition for even more … Read More

Re-configuring RISC-V Post-Silicon

How do you reconfigure system characteristics? The answer to that question is well established – through software. Make the underlying hardware general enough and use platform software to update behaviors and tweak hardware configuration registers. This simple fact drove the explosion of embedded processors everywhere … Read More

Semidynamics Unveils 3nm AI Inference Silicon and Full-Stack Systems